Document type: Title: Revision date: Revision:

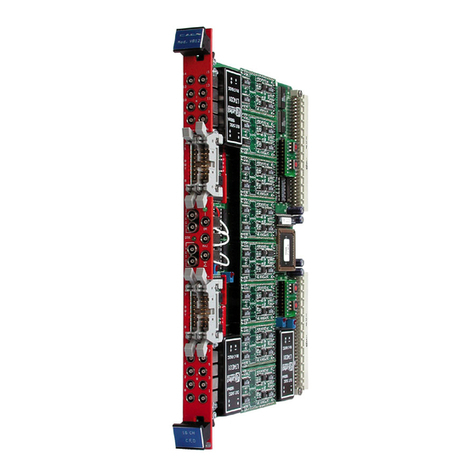

User's Manual (MUT) Mod. V1495 General Purpose VME Board 12/02/2010 8

NPO: Filename: Number of pages: Page:

00117/04:V1495.MUTx/08 V1495_REV8.DOC 42 4

4.14. USER FPGA FLASH MEMORY...........................................................................................................20

4.15. USER FPGA CONFIGURATION REGISTER..........................................................................................21

5. V1495 USER FPGA REFERENCE DESIGN KIT...................................................................................22

5.1. INTRODUCTION.......................................................................................................................................22

5.2. DESIGN KIT............................................................................................................................................22

5.2.1. V1495HAL.....................................................................................................................................22

5.2.2. COIN_REFERENCE Design.........................................................................................................23

5.3. INTERFACE DESCRIPTION........................................................................................................................25

5.3.1. Global Signals...............................................................................................................................25

5.3.2. REGISTER INTERFACE...............................................................................................................25

5.3.3. V1495 Front Panel Ports (PORT A,B,C,G) INTERFACE.............................................................26

5.3.4. V1495 Mezzanine Expansion Ports (PORT D,E,F) INTERFACE.................................................26

5.3.5. PDL Configuration Interface.........................................................................................................26

5.3.6. Delay Lines and Oscillators I/O....................................................................................................27

5.3.7. SPARE Interface............................................................................................................................27

5.3.8. LED Interface................................................................................................................................27

5.4. REFERENCE DESIGN DESCRIPTION ..........................................................................................................27

5.5. REGISTER DETAILED DESCRIPTION.............................................................................................31

5.5.1. V1495 Front Panel Ports Registers (PORT A,B,C,G)...................................................................31

5.5.2. V1495 Mezzanine Expansion Ports Registers (PORT D,E,F).......................................................32

5.5.3. Delay Selection..............................................................................................................................32

5.5.4. PDL DELAY VALUE SETTING AND READBACK......................................................................33

5.5.5. Delay Unit using PDLs..................................................................................................................34

5.5.6. Delay Unit using DLOs .................................................................................................................35

5.6. QUARTUS II WEB EDITION PROJECT ......................................................................................................36

5.7. FIRMWARE UPGRADE..............................................................................................................................42

LIST OF FIGURES

FIG.1.1: MOD.V1495 BLOCK DIAGRAM .................................................................................................................7

FIG.2.1: MODEL V1495 FRONT PANEL (WITH A395A/B/C PIGGY BACK BOARDS) ...................................................9

FIG.2.2: MULTIPIN CONNECTOR PIN ASSIGNMENT .................................................................................................11

FIG.2.3: MOD.A967 CABLE ADAPTER .................................................................................................................12

FIG.3.1: TIMERS DIAGRAM ....................................................................................................................................14

FIG.3.2: GATE PULSE EXAMPLE .............................................................................................................................14

FIG.3.3: TIMER2AND TIMER3USED TOGETHER FOR HANDLING A GATE PULSE.....................................................15

FIG.3.4: FPGA VME DIAGRAM.............................................................................................................................15

FIG.3.5: FPGA USER DIAGRAM............................................................................................................................16

FIG.4.1: INTERRUPT LEVEL REGISTER...................................................................................................................18

FIG.4.2: INTERRUPT VECTOR REGISTER ................................................................................................................19

FIG.4.3: GEOGRAPHICAL ADDRESS REGISTER ........................................................................................................19

FIG.4.4: FIRMWARE REVISION REGISTER ..............................................................................................................19