Features

•Xilinx XCKU060, in 1517 pin FCBGA package

•GR716B (initially with GR716A)

microcontroller

•SODIMM DDR3 up to 8 GiB

•SPI flash for FPGA configuration (512 Mbit),

for GR716 boot (256 Mbit), and for data

(256 Mbit)

•Power, Reset, Clock and Auxiliary circuits

•Three FMC Mezzanine expansion connectors

•Scrubbing interface for FPGA

•Backplane I/F: SpaceWire (control),

SpaceFibre (data), VPX utility management

•Frontplane I/F and drivers: 4x SpaceFibre,

2x SpaceWire, USB/FTDI UART/JTAG Links,

USB I/F to FMC

•OpenVPX compatible, 6U format, Payload

profile

Description

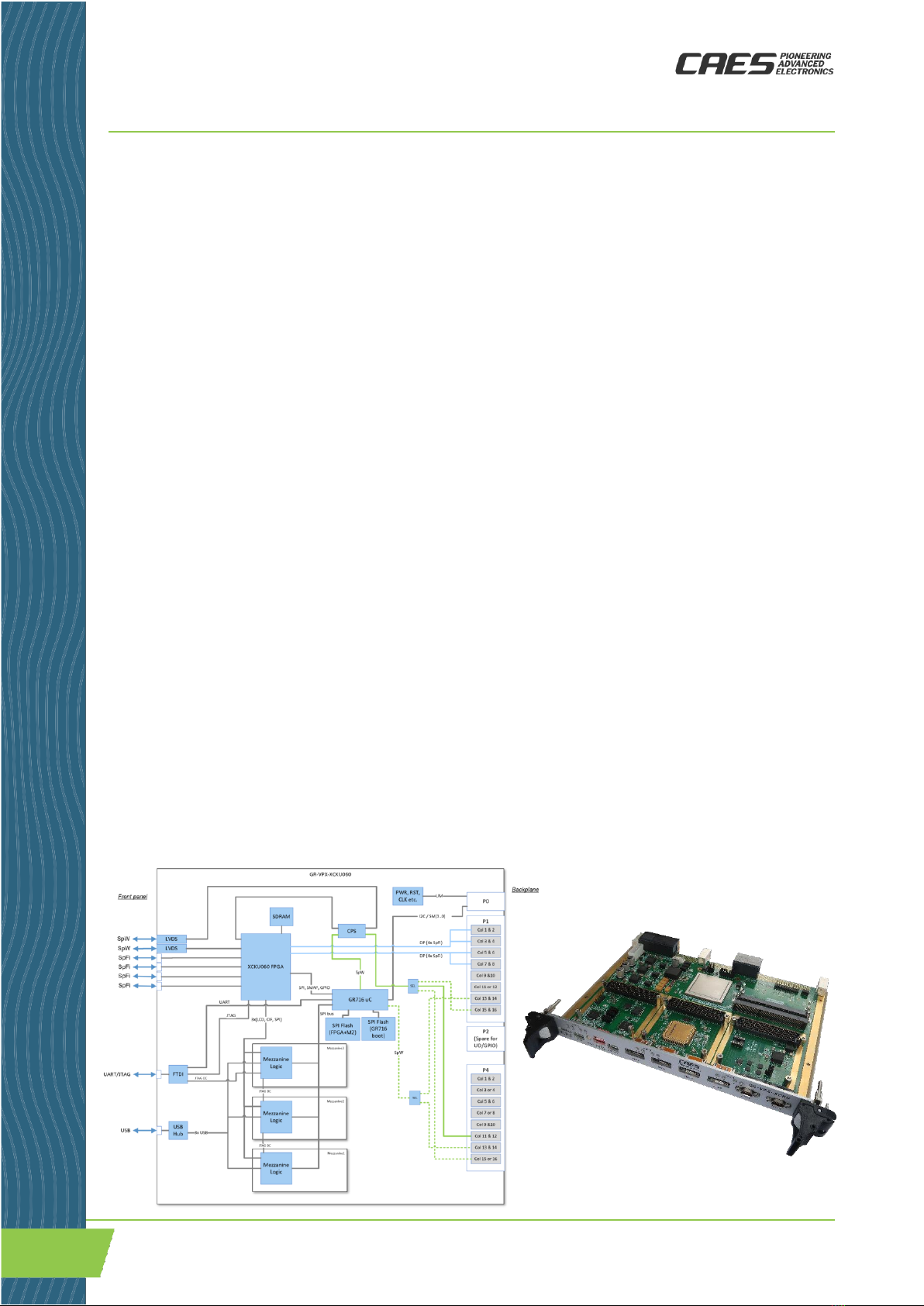

The GR-VPX-XCKU060 board features a Xilinx

Kintex Ultrascale XCKU060 FPGA and a

GR716 microcontroller acting as a supervisor

for the FPGA. The board is equipped with

three VITA 57.1 FMC connectors. It can be

operated without any Mezzanine board but is

specifically designed to be used with 1 to 3

GR-HPCB-FMC-M2 Mezzanine Boards

connected, each with a Myriad™ 2 M2450

Processor. The GR-HPCB-FMC-M2 boards are

not included with the GR-VPX-XCKU060

board.

Specifications

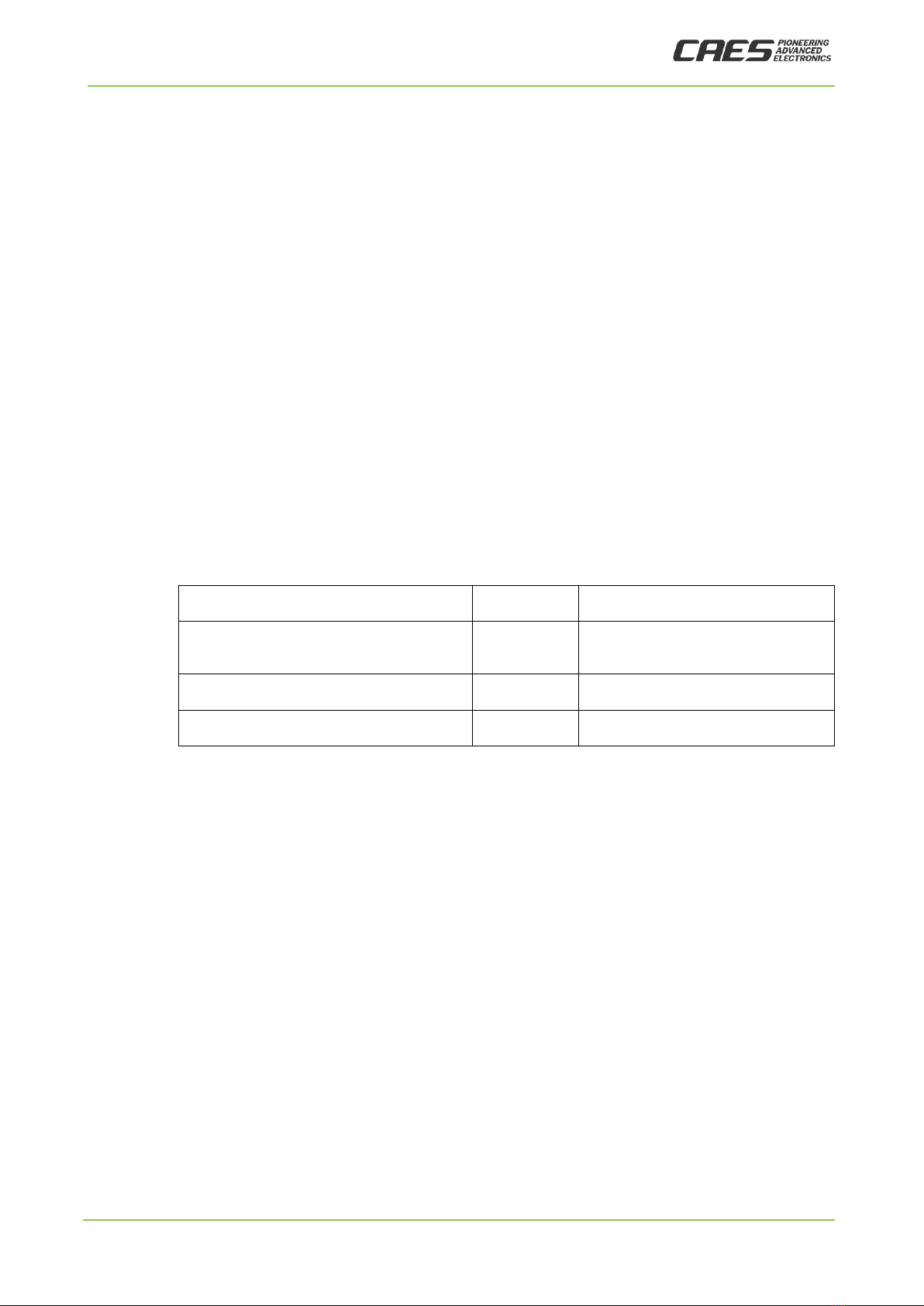

•System frequency GR716 uC: 20MHz, FPGA

XCKU060: 50 MHz

•5 x SpaceFibre links rated @ 3.125 Gbps

and 2 x SpaceWire links @ 200 Mbps

•CIF and LCD data interfaces 16-bit

running at 150 MHz. 24-bit interface

tested allowing upper bound 1.44Gb/s

full-duplex data transfer

•Typical power consumption <10W (excluding

mezzanines)

•DC supply via OpenVPX backplane connector

or via +5V/12V DC header for stand-alone

use

Applications

The board is a commercial development board for

prototyping of high-performance application such as:

•Earth Observation optical and radar payload

processing

•Multi- and hyperspectral data compression

•Visual-Based Navigation acceleration

•Video processing

•AI/ML processing, such as:

oImage segmentation (e.g. cloud

screening and removal)

oObject detection (e.g. fire detection)

oPose estimation

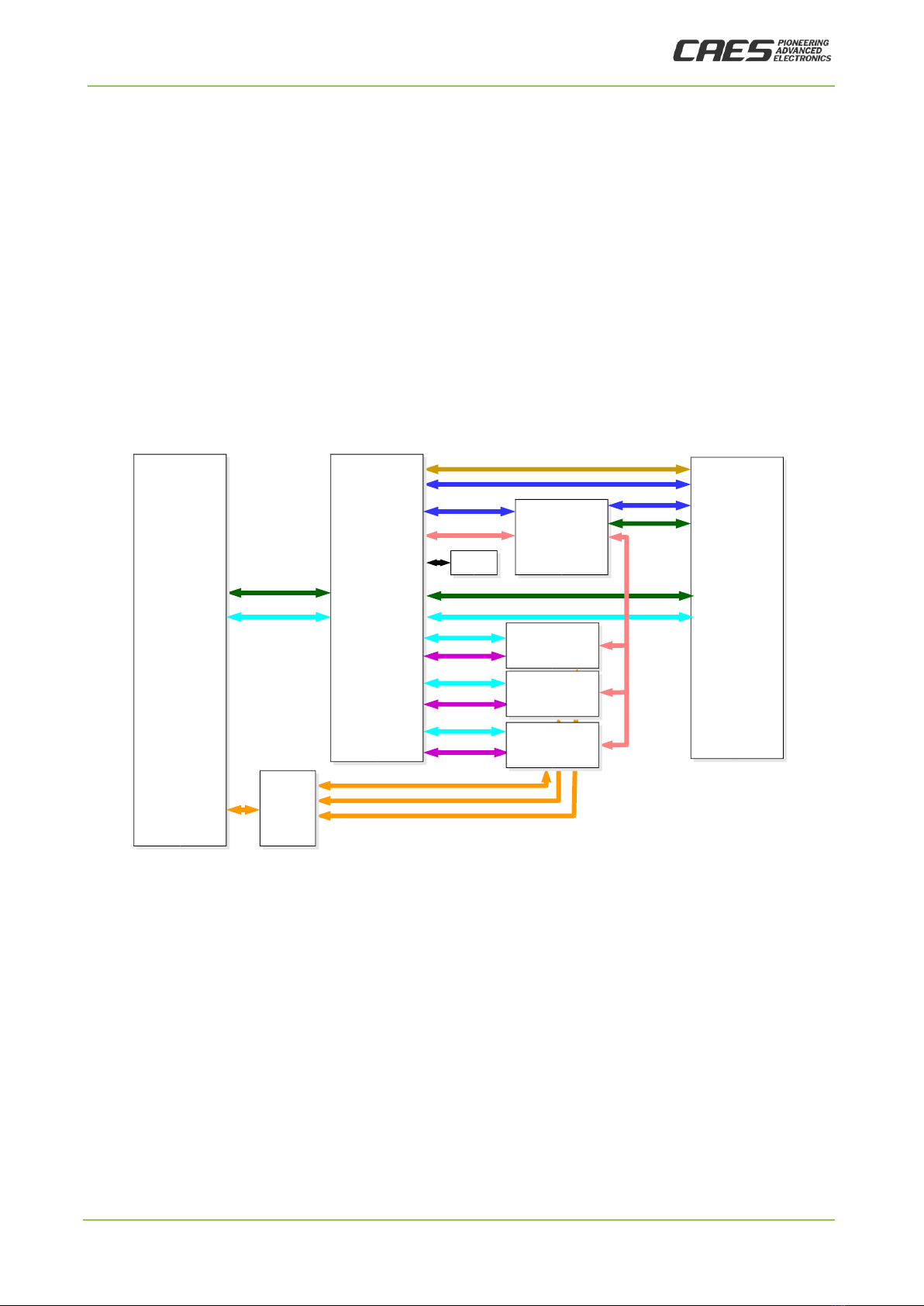

The applications can be allocated to the on-board

FPGA or shared with technology implemented in up

to three Mezzanine boards, configured either for

increased performance or for redundancy

applications. The control and supervision of the

FPGA and Mezzanine boards is handled by a rad-

hard microcontroller.