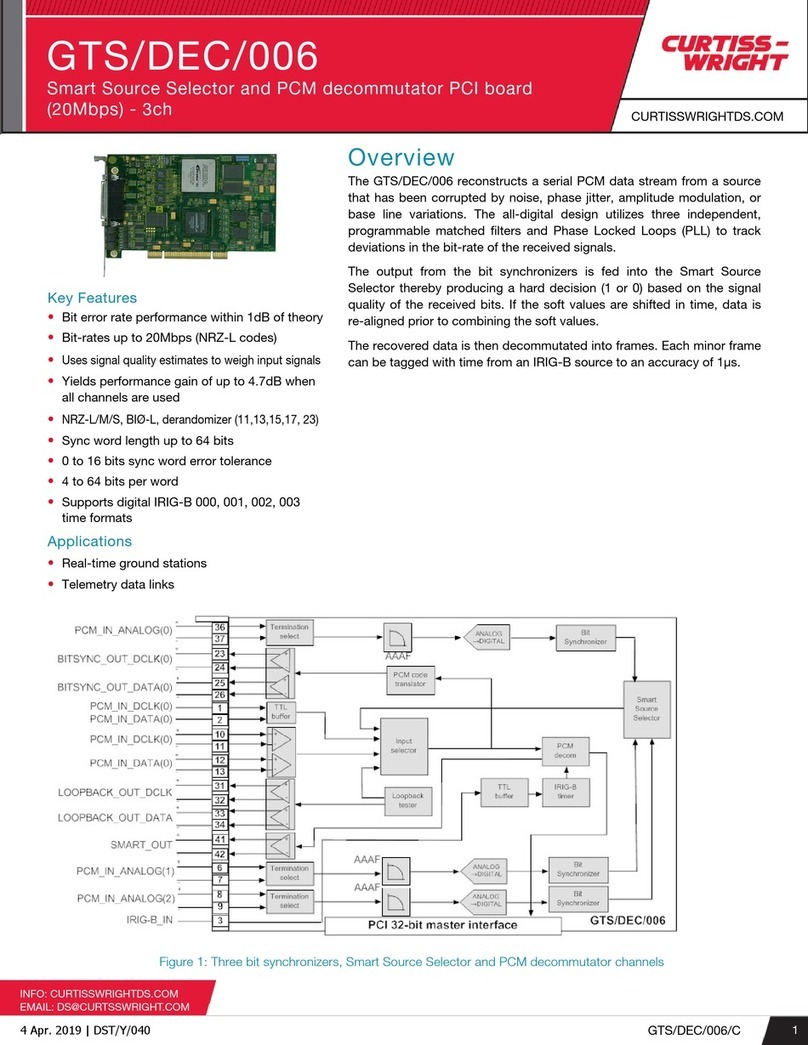

GTS/DEC/003

5

4 Apr. 2019 | DST/W/132

CURTISSWRIGHTDS.COM

Getting the most of the GTS/DEC/003

NOTE: The GTS/DEC/003 is a half-length PCI-form board and is not currently verified for use in a PCI-X slot. Voltage levels are

3.3 or 5 volts. Dimensions are: W = 0.6 inches (15.24 mm) x D = 6.9 inches (175.26 mm) × H = 4.2 inches (106.68 mm).

GTS Software Development Kit (SDK)

The GTS SDK 3 includes APIs for system definition, programming and real-time data access, and documentation with detailed

examples.

The GTS SDK 3 provides developers and system integrators with a toolkit for generating XidML® metadata files and

programming the card. It also offers real-time access to decommutated data with time tags and status registers.

Bit synchronizer performance tuning

If offset modulation is affecting performance, adjust the offset bandwidth from 100% downwards to compensate. Likewise, if

amplitude modulation is affecting performance, decrease the gain bandwidth.

Gain control bandwidth

This setting controls how quickly the automatic gain control responds to a change in amplitude; a higher setting (up to 100%)

results in a slower filter response while a smaller setting (say 20%) results in a faster response.

Offset control bandwidth

This setting controls how quickly the automatic offset control responds to a change in offset; a higher setting (up to 100%)

results in a slower filter response while a smaller setting (say 20%) results in a faster response.

Loop bandwidth filter

It is desirable to restrict loop bandwidth at higher bit rates. This is to prevent the PLL frequency from moving too far away from

the PCM clock frequency and thereby introducing jitter.

Choosing fill words

Care must be taken when choosing fill words. For example, 0xAAAA (101010…..) or 0x5555 (010101…..) can result in loss of

sync because 0xAAAA at 20Mb/s looks like 0xAAAA at 10Mb/s when using NRZ-M or NRZ-S. A fill word of, for example,

0x7E7E results in no loss of sync. By the same token, a fill word of 0xCCCC (11001100….) results in the same problem when

using 20mb/s NRZ-L. Therefore, try to avoid repetitions of these types when choosing fill words.

Loopback tester

The GTS/DEC/003 features a loopback tester, which transmits a PCM frame to allow system checks. The loopback tester

transmits frames as configured in the XidML setup. The loopback tester allows for dynamic and fixed data to be transmitted. The

TABLE 8 Decommutator settings

SETTING CHOICE DEFAULT

Input polarity True

False

True

Auto invert polarity True

False

False

Sync word mask 0 to 64 Based on size of sync word

Sync word error tolerance 0 to 16, but less than 25% of sync word bits 0

PCM clock phase [°] 0° / 90° / 180° / 270° 0°