GTS/DEC/006

9

4 Apr. 2019 | DST/Y/040

CURTISSWRIGHTDS.COM

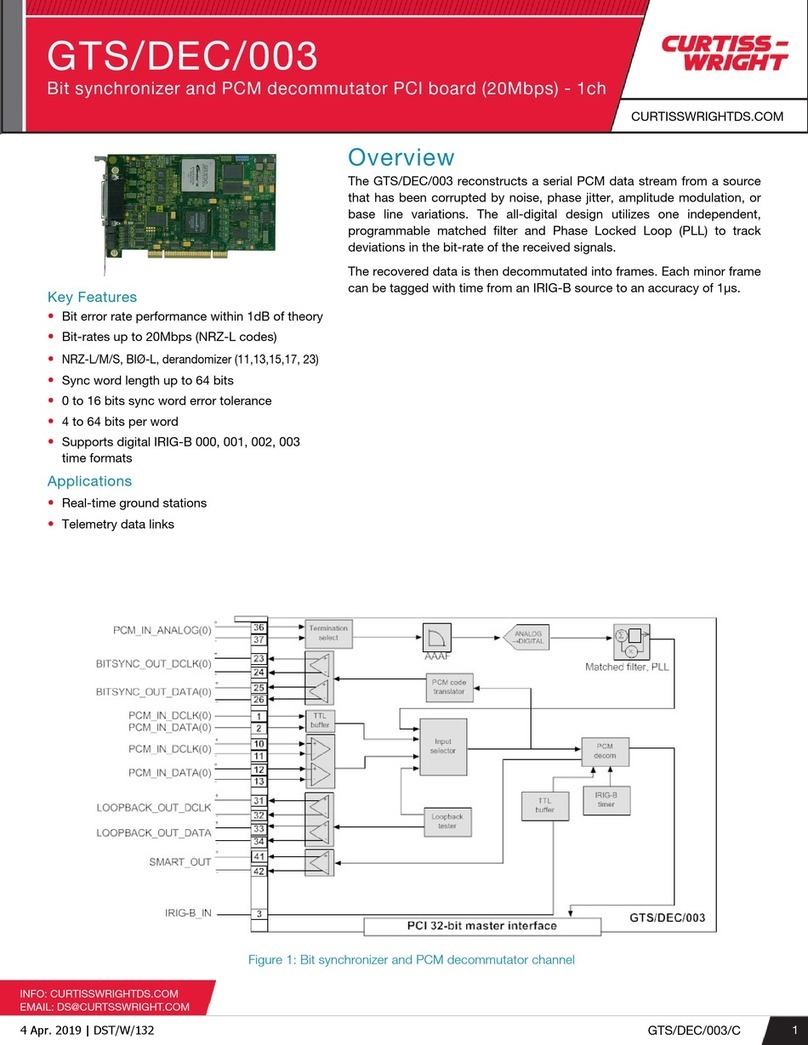

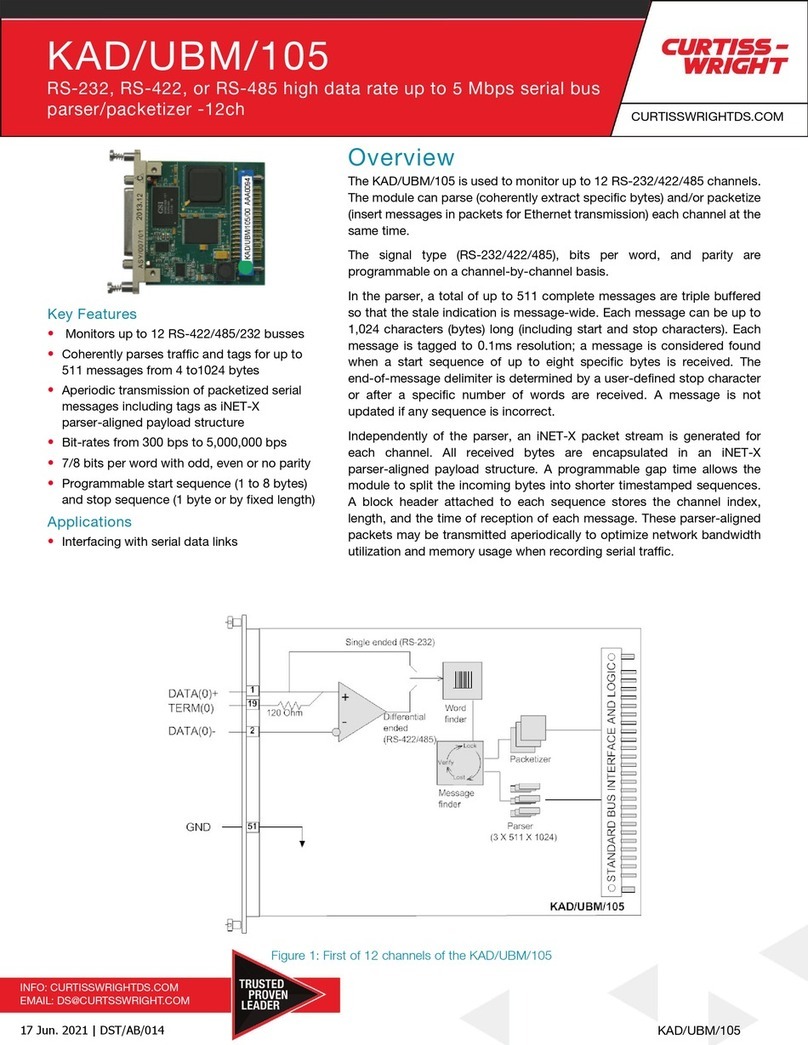

Connector pinout of the GTS/DEC/006

Figure 5: Connector pins

PIN NAME SEE SPECIFICATIONS TABLE COMMENT

1PCM_IN_DCLK(0) BTTL inputs PCM clock

2PCM_IN_DATA(0) BTTL inputs PCM data

3IRIG-B_IN BTTL inputs IRIG-B-002 input

4DNC Do not connect

5GND GTS-500 internal ground

6PCM_IN_ANALOG(1)+ Bit synchronizer inputs Differential ended bit synchronizer input for channel 1

7PCM_IN_ANALOG(1)- Bit synchronizer inputs Differential ended bit synchronizer input for channel 1

8PCM_IN_ANALOG(2)+ Bit synchronizer inputs Differential ended bit synchronizer input for channel 2

9PCM_IN_ANALOG(2)- Bit synchronizer inputs Differential ended bit synchronizer input for channel 2

10 PCM_IN_DCLK(0)+ RS-422 inputs Differential ended PCM decommutator clock input

11 PCM_IN_DCLK(0)- RS-422 inputs Differential ended PCM decommutator clock input

12 PCM_IN_DATA(0)+ RS-422 inputs Differential ended PCM decommutator data input

13 PCM_IN_DATA(0)- RS-422 inputs Differential ended PCM decommutator data input

14 DNC Do not connect

15 DNC Do not connect

16 GND GTS-500 internal ground

17 GND GTS-500 internal ground

18 DNC Do not connect

19 DNC Do not connect

20 GND GTS-500 internal ground

21 DNC Do not connect

22 GND GTS-500 internal ground

23 BITSYNC_OUT_DCLK(0)+ RS-422 outputs Differential ended bit synchronizer clock output

24 BITSYNC_OUT_DCLK(0)- RS-422 outputs Differential ended bit synchronizer clock output

25 BITSYNC_OUT_DATA(0)+ RS-422 outputs Differential ended bit synchronizer data output

26 BITSYNC_OUT_DATA(0)- RS-422 outputs Differential ended bit synchronizer data output

27 DNC Do not connect

28 DNC Do not connect

29 DNC Do not connect

30 DNC Do not connect

31 LOOPBACK_OUT_DCLK+ RS-422 outputs Differential ended loopback tester clock output

32 LOOPBACK_OUT_DCLK- RS-422 outputs Differential ended loopback tester clock output

33 LOOPBACK_OUT_DATA+ RS-422 outputs Differential ended loopback tester data output

34 LOOPBACK_OUT_DATA- RS-422 outputs Differential ended loopback tester data output

35 GND GTS-500 internal ground

36 PCM_IN_ANALOG(0)+ Bit synchronizer inputs Differential ended bit synchronizer input for channel 0

37 PCM_IN_ANALOG(0)- Bit synchronizer inputs Differential ended bit synchronizer input for channel 0

38 GND GTS-500 internal ground

39 DNC Do not connect

40 DNC Do not connect

41 SMART_OUT+ RS-422 outputs Differential ended smart output (user configurable)

42 SMART_OUT- RS-422 outputs Differential ended smart output (user configurable)

43 DNC Do not connect

44 DNC Do not connect