5

S-101

特殊操作方法

1. 初期化

※ファンクション、VOL 及び DVD メカ (RL-874) 等の

データを初期化します。

(1) ACコードがコンセントより外れていることを確認

します。(ACOFF)

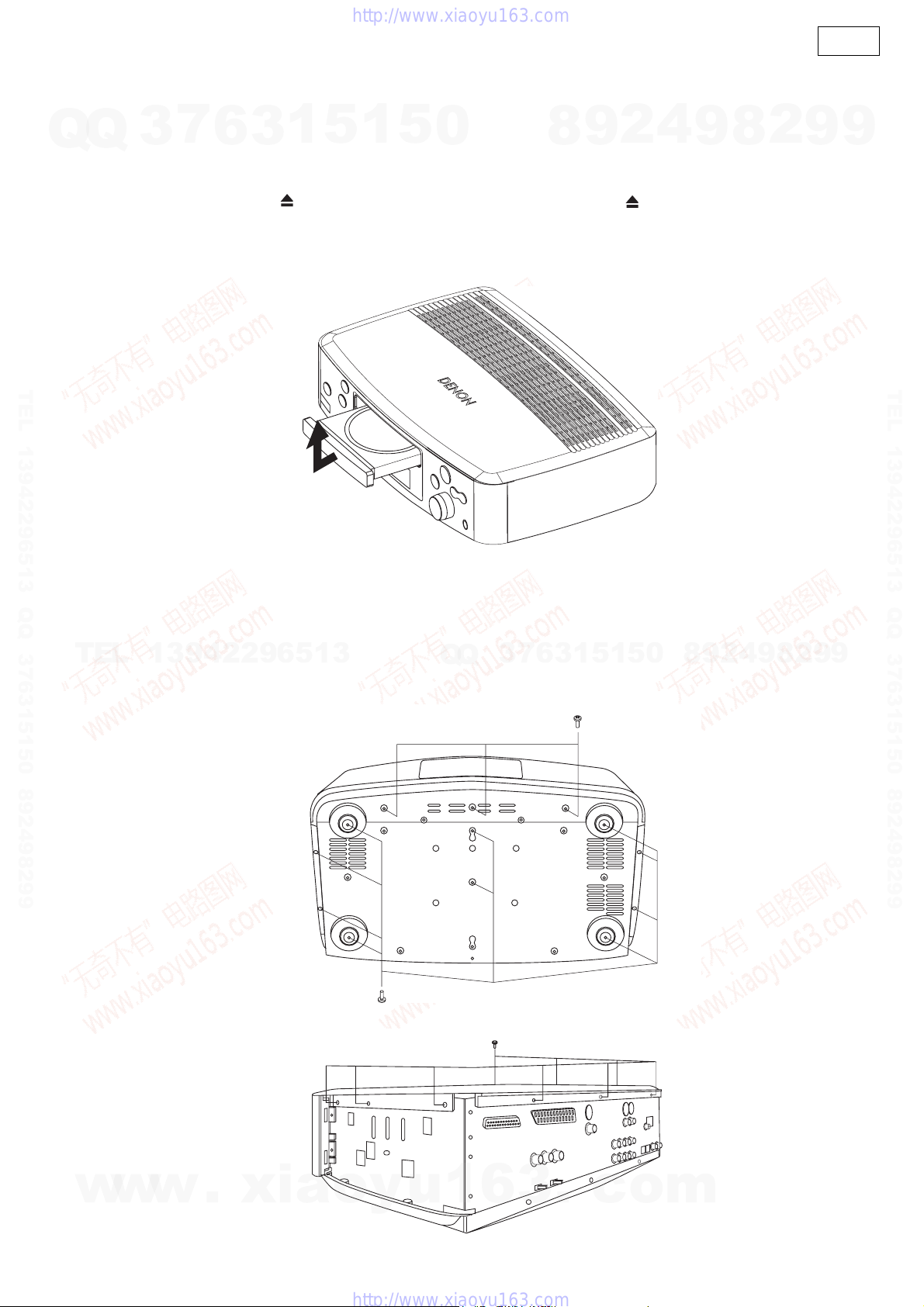

(2) 本体の FUNCTION ボタンと OPEN/CLOSE( ) ボタ

ンを押しながら、AC コードをコンセントに接続

(ACON) します。

(3) ディスプレイと LED の全点灯を確認したら、本体

の FUNCTION ボタンと OPEN/CLOSE( ) ボタンを

離します。

(4) 約 3 秒後、ディスプレイに "INITIALIZE" が表示され

ます。

(5) 初期化完了 ("INITIALIZE" 消灯 ) 後、FUNCTION は

"DVD"、VOL位置は-∞(表示は"---dB")となります。

2. システムチェックモード

※バージョン表示等をおこないます。

(1) STANDBY 時、本体の STOP( )ボタンと A.FWD

( )ボタンを押しながら、ON/STANDBY ボタ

ンを押します。

(2) リモコン(RC-1007)の STATUS ボタンを押すこと

により

時間(TIME)→システムマイコンのバージョン(SYS

Ver) →システムマイコンのバージョンアップ日

(SYSDate)→DSP のバージョン (DSPVer) → DSP

のバージョンアップ日(DSPDate)→ドライブマイ

コンのバージョンアップ日 (DrDate) →ESS のバー

ジョン (EssVer) → Ess のバージョンアップ日 (Ess

Date) →地域番号 (RegionNo.)

の順に表示されます。

(3) 解除するにはAC コードを抜きます。(ACOFF)

( 注 1) DVD メカのドライブバージョン表示、ESS

のバージョン表示については、1 度ファン

クッションを DVD にしないと表示されま

せん。

Special operating procedures

1. Initialization

※This initializes the data for the function, volume,

DVD mechanism (RL-874), etc.

(1) Check that the AC cord is disconnected from the

power outlet. (AC OFF)

(2) While pressing the FUNCTION and OPEN/CLOSE

( ) buttons on the main unit, plug the AC cord into

the power outlet. (AC ON)

(3) Check that the entire display and all the LEDs light,

then release the FUNCTION and OPEN/CLOSE

()buttons.

(4) After about 3 seconds, "INITIALIZE" appears on the

display.

(5) After initialization is complete (when "INITIALIZE"

turns off), the function is set to "DVD" and the vol-

ume level is set to -∞("-dB" is displayed).

2. System check mode

※Use this to display the version information, etc.

(1) In the standby mode, while pressing the STOP ( )

and A.FWD ( ) buttons on the main unit, press

the ON/STANDBY button.

(2) Press the STATUS button on the remote control

unit (RC-1007) to display the following information,

in this order: Time (TIME) →System microproces-

sor version (SYS Ver) →Date of system micropro-

cessor version updating (SYS Date) →DSP ver-

sion (DSP Ver) →Date of DSP version updating

(DSP Date)→Date of drive microprocessor version

updating (Dr Date) →ESS version (Ess Ver) →

Date of ESS version updating (Ess Date) →Region

number (Region No.)

(3) To cancel, unplug the AC cord. (AC OFF)

NOTE 1: The DVD mechanism driver version and

ESS version are not displayed unless the

function is once set to DVD.

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com