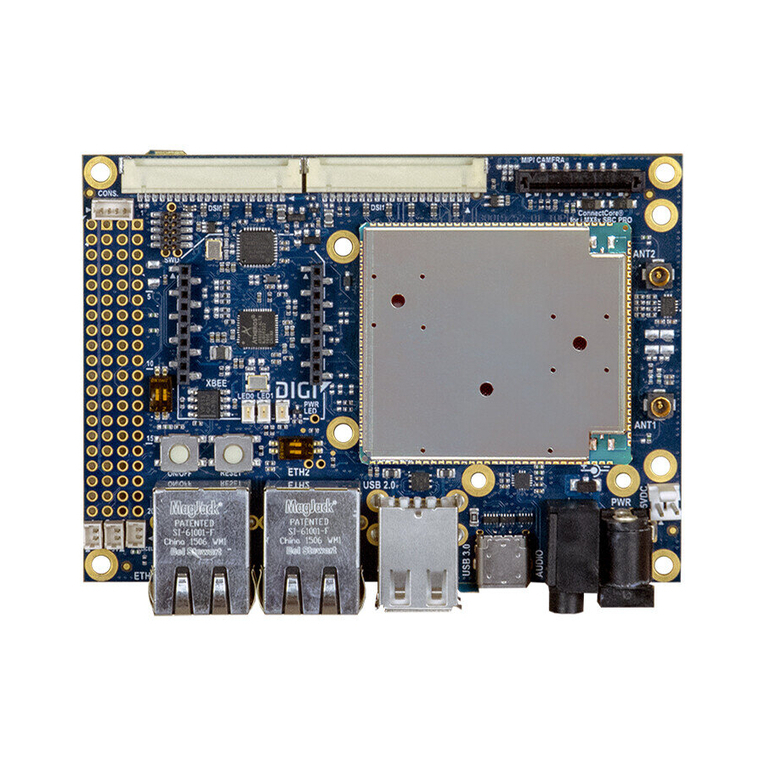

Schematics design checklist Naming and signal conventions

ConnectCore 6UL Hardware Design Guidelines 9

☑Item Description

4. Boot

configuration

lines buffer

Boot configuration lines are latched during booting for configuring the

boot process of the SOM. Digi recommends you add a buffer to protect

these lines during booting. External circuitry and peripherals connected

to these lines can modify the expected value when system is booting, so

that the process can fail. See the Schematic: boot configuration lines

used on the ConnectCore 6UL SBC PRO reference design.

Eight additional BOOT_CFG lines are configured inside the module. These

lines are LCD_DATA[9:15]. Place another buffer for these lines if you

expect to have external circuitry/peripherals modifying their values.

5. LCD_DATA23

line

configuration

This line is one of the GPIOs latched during booting and is used to

configure one of the Boot Configuration bits (BOOT_CFG4[7]). It enables

an infinite loop debug mode. For proper operation, make sure this line is

not pulled-high during booting.

MCA

1.MCA_RESET Input reset line of the system. Connect a 100K pull-up to VCC_MCA.

2. SWD_

CLK/PWR_IO

Input power on/off - suspend line of the system. Connect a 100K pull-up

to VCC_MCA.

3. Isolate VCC_

MCA power

domains

As much as possible, try not to mix the VCC_MCA power domain with the

rest of the power domains of the system. The ConnectCore 6UL SBC

Express/PRO designs use an MCA GPIO to manage the reset line of the

LAN8720Ai PHY (powered from 3V3_EXT). This configuration resulted in

some unexpected backdrive currents.

Console debug port

1.UART5 The default U-Boot loaded in the modules from manufacturing configures

the UART5 as the console debug port. This console port can be changed

to any other UART in the system, but Digi recommends you use this

UART5 as the console port so no additional effort (such as compiling a

new U-Boot, loading it through USB, etc.) are required.

I2C

1.I2C1 bus Do not use the I2C1 bus to communicate with external peripherals. This

bus is used internally in the module for interconnecting critical devices

(CPU, MCA, PMIC).

2.I2C pull-ups Add external pull-ups to the clock and data lines of the I2C buses. You will

typically use 4.7K resistors.

GPIOs

1.GPIO5 ring GPIO5_x I/Os are supplied from VDD_SNVS_IN (3.0V). Do not overdrive

them with 3.3V.