SpaceWire Monitor User Manual

Embedded Solutions v

Table of Contents

Design Revision History ....................................................................................................................................... 1

Manual Revision History ...................................................................................................................................... 1

Key Product Features .......................................................................................................................................... 2

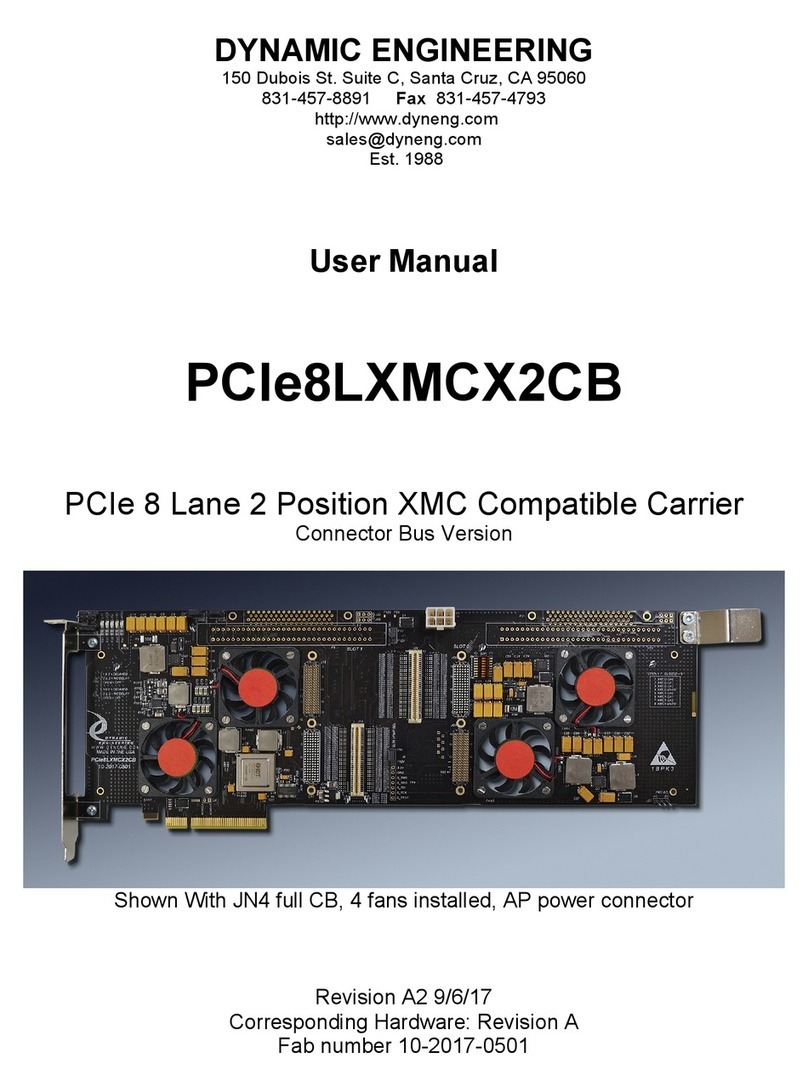

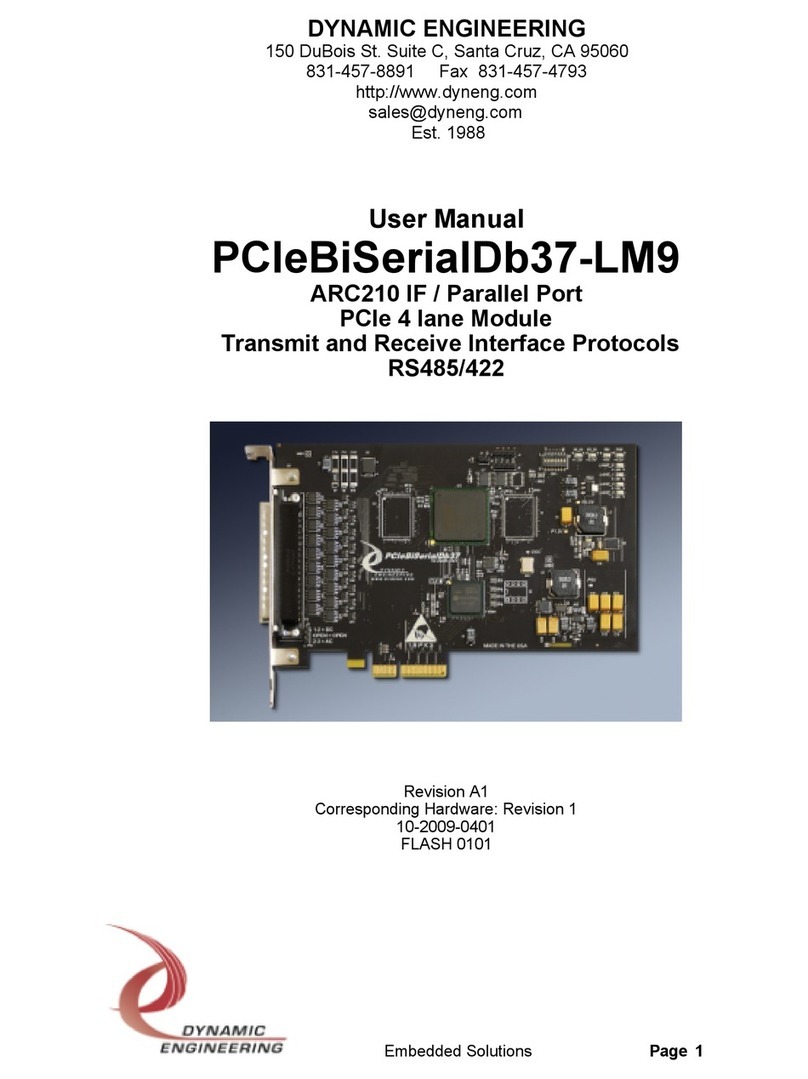

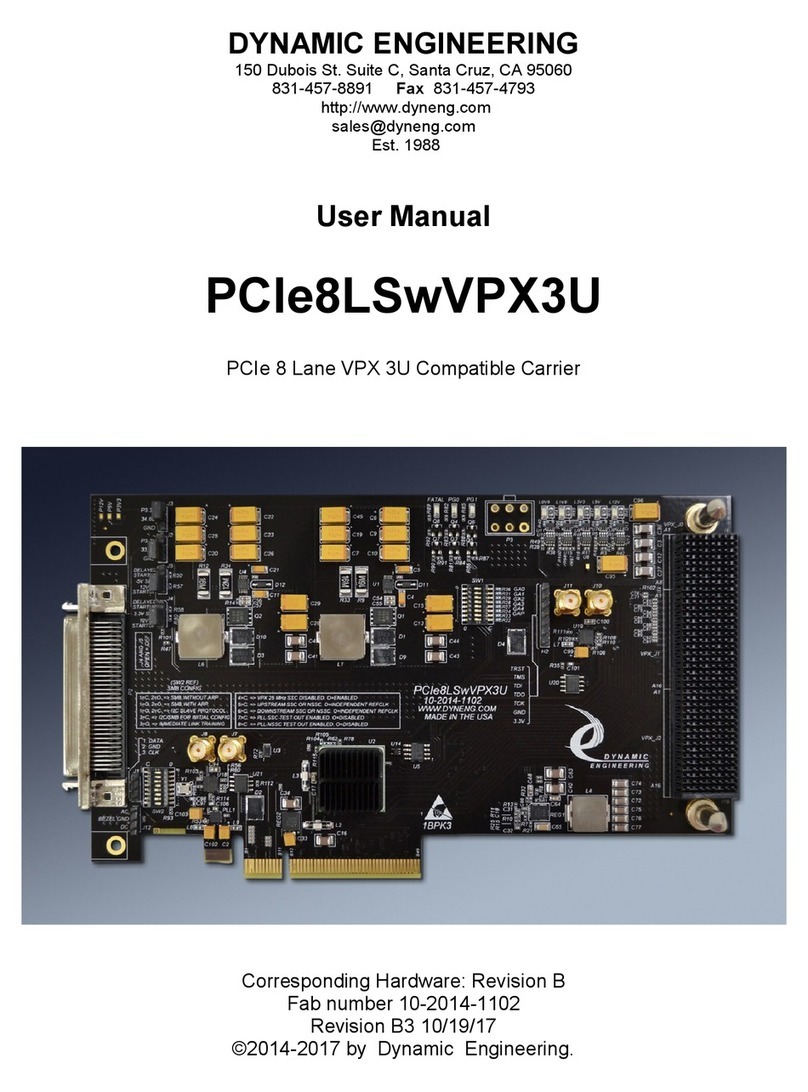

Product Description .............................................................................................................................................. 2

Product Specifications .......................................................................................................................................... 3

Construction and Reliability .................................................................................................................................. 3

Installation and Interfacing Guidelines ................................................................................................................. 4

Installation ......................................................................................................................................................... 4

ESD .................................................................................................................................................................. 4

Start-Up ............................................................................................................................................................ 4

Guidelines ......................................................................................................................................................... 4

Grounds ........................................................................................................................................................ 4

Power Supply ................................................................................................................................................ 4

Thermal Considerations .................................................................................................................................... 4

Theory of Operation ............................................................................................................................................. 5

Address Maps and Register Definitions ............................................................................................................... 6

Register Definitions ........................................................................................................................................... 7

SpaceWire Base Control Register .................................................................................................................... 7

SpaceWire User Switch Port ............................................................................................................................ 8

SpaceWire PLL Data FIFO ............................................................................................................................... 9

SpaceWire PLL Status Register ....................................................................................................................... 9

SpaceWire Channel Control Register ............................................................................................................. 10

SpaceWire Channel Status Register .............................................................................................................. 13

SpaceWire Channel Read DMA Pointer Port ................................................................................................. 15

SpaceWire Channel RX FIFO Data Count Port .............................................................................................. 16

SpaceWire RX Packet-Length FIFO Ports ..................................................................................................... 16

SpaceWire Channel RX Almost Full Level Register ....................................................................................... 17

SpaceWire Channel RX Packet FIFO Full Control Register ........................................................................... 17

Warranty and Repair .......................................................................................................................................... 19

Service Policy ................................................................................................................................................. 19

Out-of-Warranty Repairs ................................................................................................................................. 19

Contact ........................................................................................................................................................... 19

Ordering Information .......................................................................................................................................... 20

Glossary ............................................................................................................................................................. 21

Tables

Table 1: Flash and Software Revision History ..................................................................................................... 1

Table 2: Manual Revision History ........................................................................................................................ 1

Table 3: Product Specifications ............................................................................................................................ 3

Table 4:SpaceWire Address Map ........................................................................................................................ 6

Table 5: SpaceWire Base Control Register ......................................................................................................... 7

Table 6: SpaceWire User Switch Port .................................................................................................................. 8

Table 7: SpaceWire Configurations ..................................................................................................................... 8

Table 8: SpaceWire PLL Data FIFO .................................................................................................................... 9

Table 9: SpaceWire PLL Status Register ............................................................................................................. 9

Table 10: SpaceWire Channel Control Register ................................................................................................ 10