Embedded Solutions Page 10

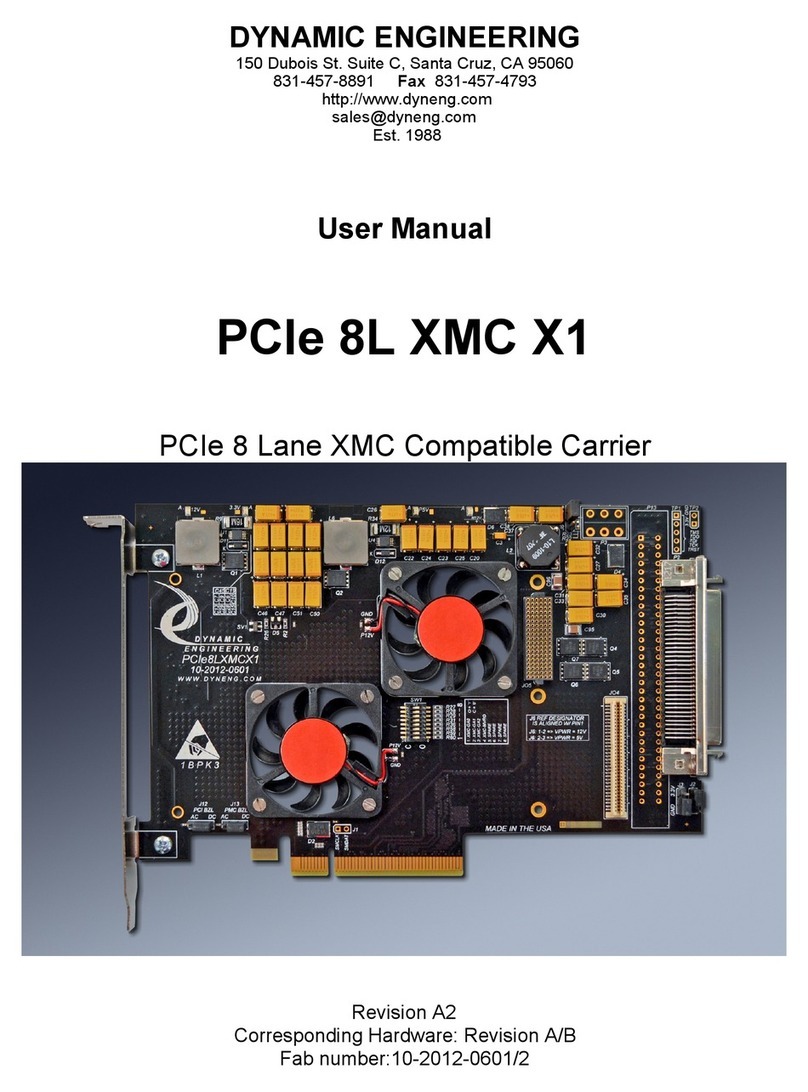

XMC Module Backplane IO Interface Pin Assignment

The figure below gives the pin assignments for the XMC Module IO Interface – from Jn4

and/or Jn6 to the PCIe8LXMCX2CB connectors. Also see the User Manual for your

XMC board for more information. Please note that P2 or P13, P7 or P5 are installed not

both.

DIN IDC [P13,P5] SCSI II [P2,P7] Sig/Sig Jn4 Jn6

A1 C1 1 35 0N/0P 3 1 B1 A1

A2 C2 2 36 1N/1P 4 2 E1 D1

A3 C3 3 37 2N/2P 7 5 C2 C1

A4 C4 4 38 3N/3P 8 6 F2 F1

A5 C5 5 39 4N/4P 11 9 B3 A3

A6 C6 6 40 5N/5P 12 10 E3 D3

A7 C7 7 41 6N/6P 15 13 C4 C3

A8 C8 8 42 7N/7P 16 14 F4 F3

A9 C9 9 43 8N/8P 19 17 B5 A5

A10 C10 10 44 9N/9P 20 18 E5 D5

A11 C11 11 45 10N/10P 23 21 C6 C5

A12 C12 12 46 11N/11P 24 22 F6 F5

A13 C13 13 47 12N/12P 27 25 B7 A7

A14 C14 14 48 13N/13P 28 26 E7 D7

A15 C15 15 49 14N/14P 31 29 C8 C7

A16 C16 16 50 15N/15P 32 30 F8 F7

A17 C17 17 51 16N/16P 35 33 B9 A9

A18 C18 18 52 17N/17P 36 34 E9 D9

A19 C19 19 53 18N/18P 39 37 C10 C9

A20 C20 20 54 19N/19P 40 38 F10 F9

A21 C21 21 55 20N/20P 43 41 B11 A11

A22 C22 22 56 21N/21P 44 42 E11 D11

A23 C23 23 57 22N/22P 47 45 C12 C11

A24 C24 24 58 23N/23P 48 46 F12 F11

A25 C25 25 59 24N/24P 51 49 B13 A13

A26 C26 26 60 25N/25P 52 50 E13 D13

A27 C27 27 61 26N/26P 55 53 B15 A15

A28 C28 28 62 27N/27P 56 54 E15 D15

A29 C29 29 63 28N/28P 59 57 B17 A17

A30 C30 30 64 29N/29P 60 58 E17 D17

A31 C31 31 65 30N/30P 63 61 B19 A19

A32 C32 32 66 31N/31P 64 62 E19 D19

33 67 Open, +3 or GND via J2,19 silk screen defined

34 68 Open, +3 or GND via J3,20

FIGURE 1 PCIE8LXMCX2CB JN4/JN6 INTERFACE STANDARD

Read table:

P13-C1 = P2-35 = Pn4-1 P13-A1 = P2-1 = Pn4-3 etc.

With Jn6: Pins: A, B, D, E of rows 2, 4, 6, 8, 10, 12 ,14, 16, 18 are grounded

Effective connections with RIO column of resistors installed and both connector

selectors.