AT84AS0003-EB Evaluation Kit User Guide 1-1

0905C–BDC–09/07

Section 1

Introduction

1.1 Scope

The AT84AS003-EB Evaluation Kit is designed to facilitate the evaluation and charac-

terization of the AT84AS003 10-bit 1.5 Gsps ADC with 1:2/4 DMUX up to its 3 GHz full

power input bandwidth and up to 1.5 Gsps.

The AT84AS003-EB Evaluation Kit includes:

The 10-bit 1.5 Gsps ADC with 1:2/4 DMUX Evaluation board including the

AT84AS003 device soldered and a heat sink screwed on the board

10 SMA caps for CLK, CLKN, VIN, VINN, DAI, DAIN, DAO, DAON, DRRB and

AsyncRST signals

12 jumpers for ADC and DMUX function settings (SDAEN, B/GB, PGEB, RS, BIST,

CLKTYPE, DRTYPE, SLEEP, STAGG, DAEN)

The user guide uses the AT84AS003-EB Evaluation Kit as an evaluation and demon-

stration platform and provides guidelines for its proper use.

1.2 Description

The AT83AS003-EB evaluation board is very straightforward as it only implements the

AT84AS003 10-bit 1.5 Gsps ADC/DMUX device, SMA connectors for the sampling

clock, analog inputs and reset inputs accesses and 2.54 mm pitch connectors compati-

ble with high-speed acquisition system probes.

To achieve optimal performance, the AT84AS003-EB evaluation board was designed in

a 8-metal-layer board with RO4003 200 µm and FR4 HTG epoxy dielectric materials.

The board implements the following devices:

The 10-bit 1.5 Gsps ADC with 1:2/4 DMUX evaluation board with the AT84AS003

ADC soldered and a heat sink screwed on the board

10 SMA caps for CLK, CLKN, VIN, VINN, DAI, DAIN, DAO, DAON, DRRB and

AsyncRST signals

12 jumpers for ADC and DMUX function settings (SDAEN, B/GB, PGEB, RS, BIST,

CLKTYPE, DRTYPE, SLEEP, STAGG, DAEN)

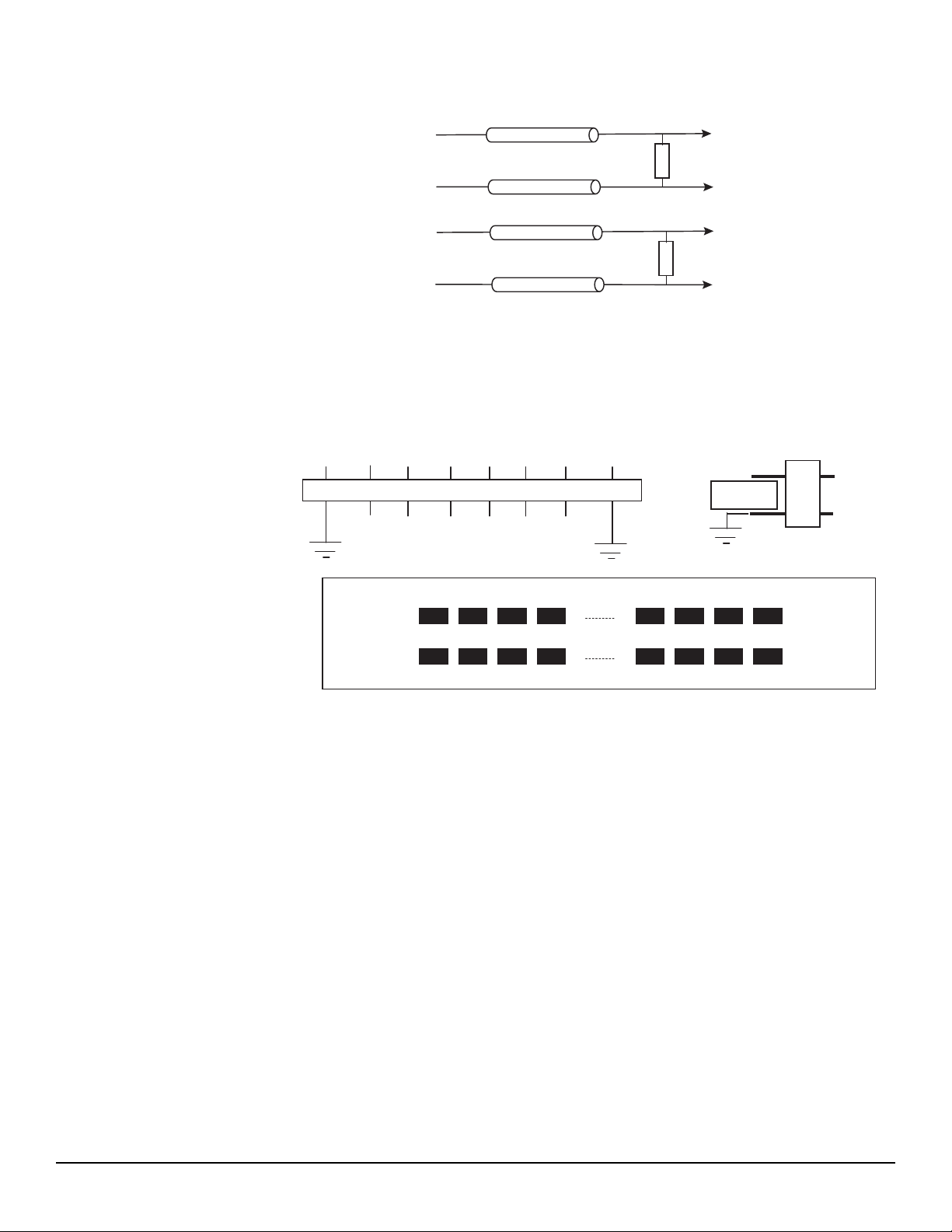

2.54 mm pitch connectors for the digital outputs, compatible with high speed

acquisition system probes

Banana jacks for the power supply accesses and the die junction temperature

monitoring functions (2 mm)