AT84CS001-EB Evaluation Board User Guide i

0904C–BDC–09/07

Table of Contents

Section 1

Introduction ............................................................................................. 1

1.1 Scope ..............................................................................................................1

1.2 Description ......................................................................................................1

Section 2

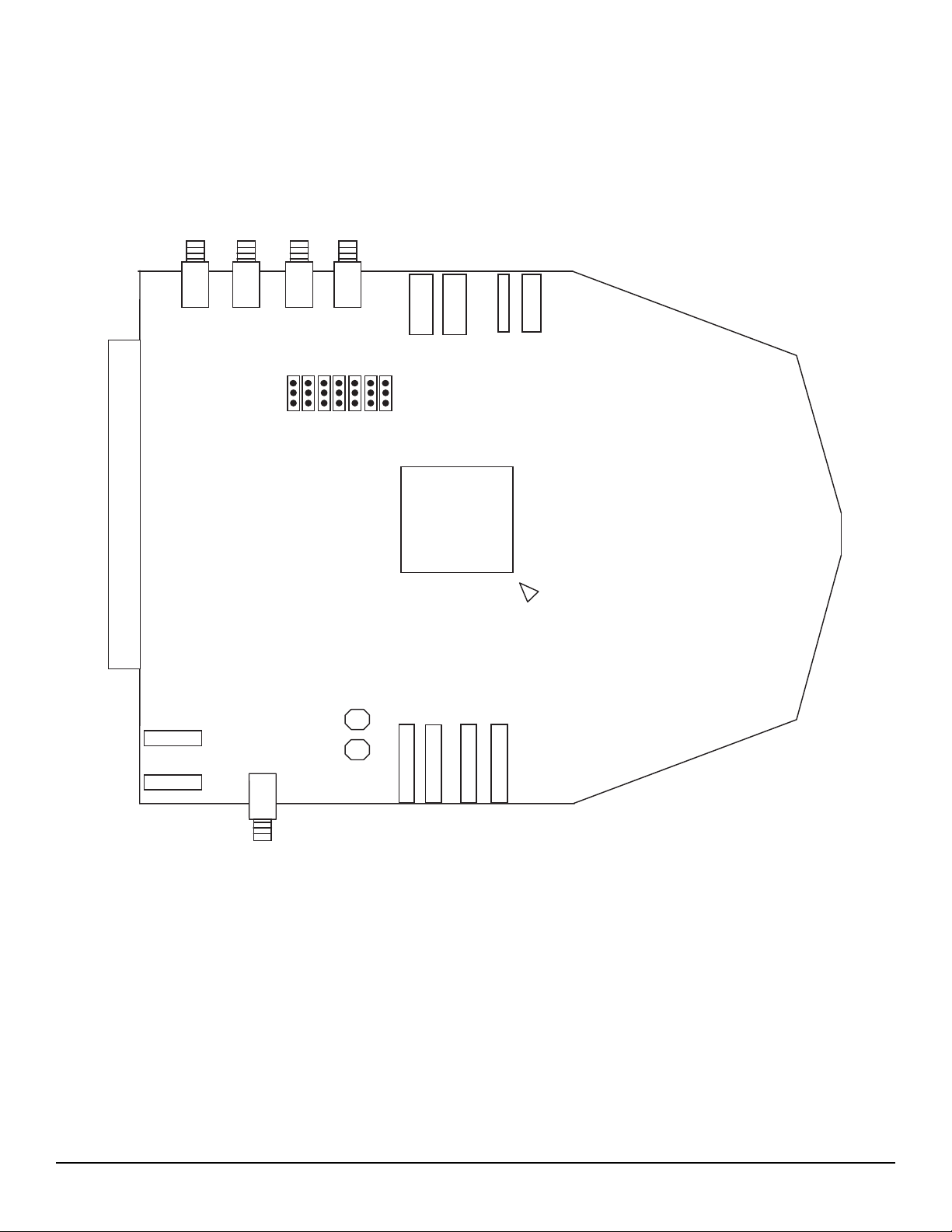

Hardware Description ............................................................................. 1

2.1 Board Structure 1

2.2 Data and Clock Input Accesses ......................................................................2

2.3 Digital Output 2

2.4 ASYNCRST .................................................................................................... 3

2.5 Standalone Delay Cell .................................................................................... 3

2.6 DMUX Functions............................................................................................. 3

2.7 Power Supplies ...............................................................................................3

Section 3

Operating Characteristics ....................................................................... 1

3.1 Introduction .....................................................................................................1

3.2 Operating Procedure ......................................................................................1

3.3 Electrical Characteristics ................................................................................2

Section 4

Application Information ........................................................................... 1

4.1 Introduction ..................................................................................................... 1

4.2 Input Data .......................................................................................................1

4.3 Digital Outputs ................................................................................................ 1

4.4 DMUX Functions .............................................................................................2

4.4.1 ASYNCRST ..............................................................................................2

4.4.2 CLKDACTRL ............................................................................................2

4.4.3 DACTRL ...................................................................................................3

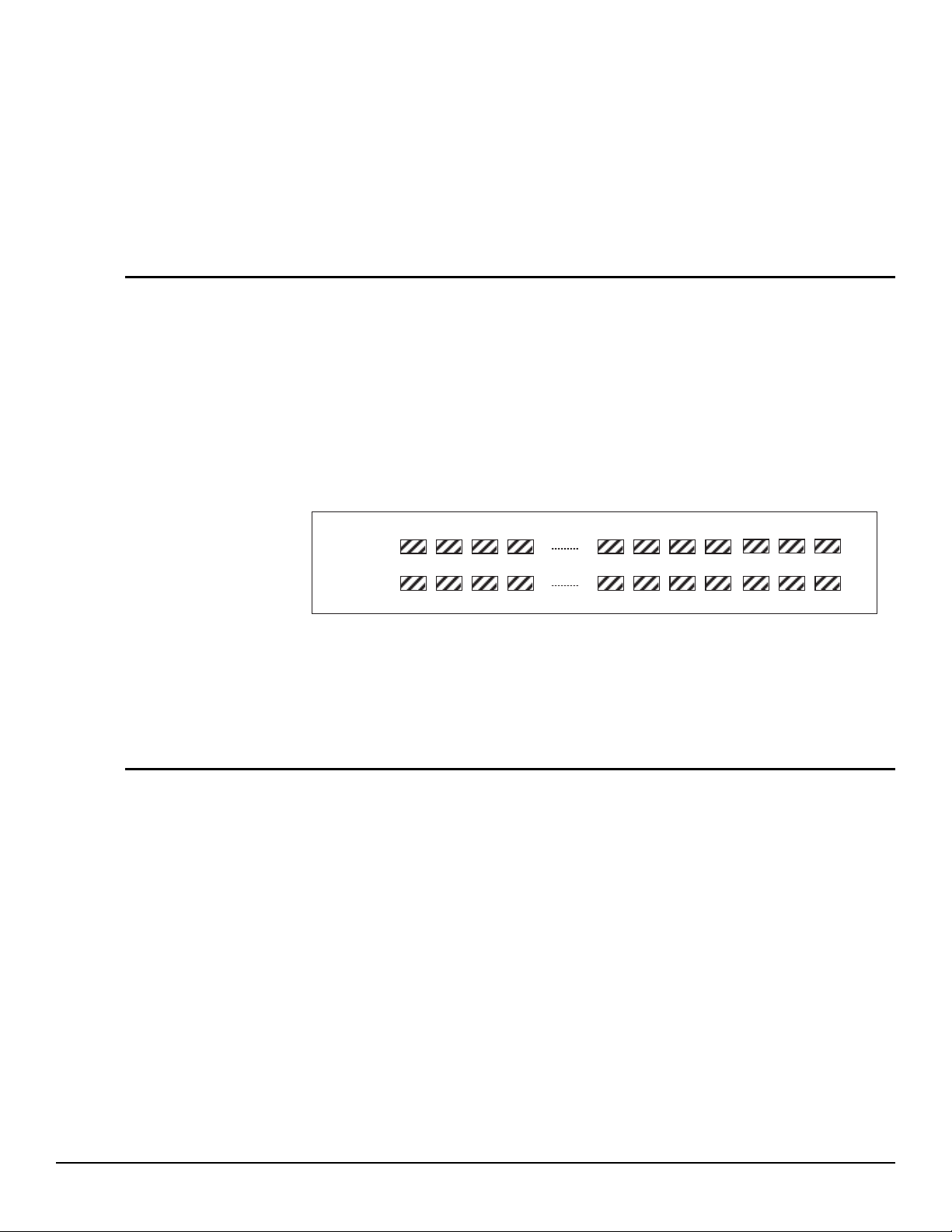

4.4.4 RS, DRTYPE, DAEN, BIST, CLKTYPE, SLEEP, STAGG .......................4

4.5 Test bench Description ...................................................................................6

Section 5

Package Information ............................................................................... 1

5.1 AT84CS001 Pinout .........................................................................................1

5.2 Package Outline .............................................................................................5

Section 6