Layout Information

2-2 TSEV8308500 Evaluation Board User Guide

0968D–BDC–01/09

e2v semiconductors SAS 2009

2.4 Power Supplies The bottom metal layer 7 is dedicated to the power supply traces (VEEA, VEED, VEET, VCC,

VDD, VPLUSD).

The supply traces are approximately 6 mm wide in order to present low impedance, and

are surrounded by a ground plane connected to the two inner ground planes.

The Analog and Digital negative power supply traces are independent, but the possibil-

ity exists to short-circuit both supplies on the top metal layer.

No difference in ADC high speed performance is observed when connecting both nega-

tive supply planes together. Obviously one single negative supply plane could be used

for the circuit.

Each power supply incoming is bypassed by a 1 µF Tantalum capacitor in parallel with

1 nF chip capacitor.

Each power supply access is decoupled very close to the device by a 10 nF and 100 pF

surface mount chip capacitors in parallel.

Note: The decoupling capacitors are superposed. In this configuration, the 100 pF capacitors

must be mounted first.

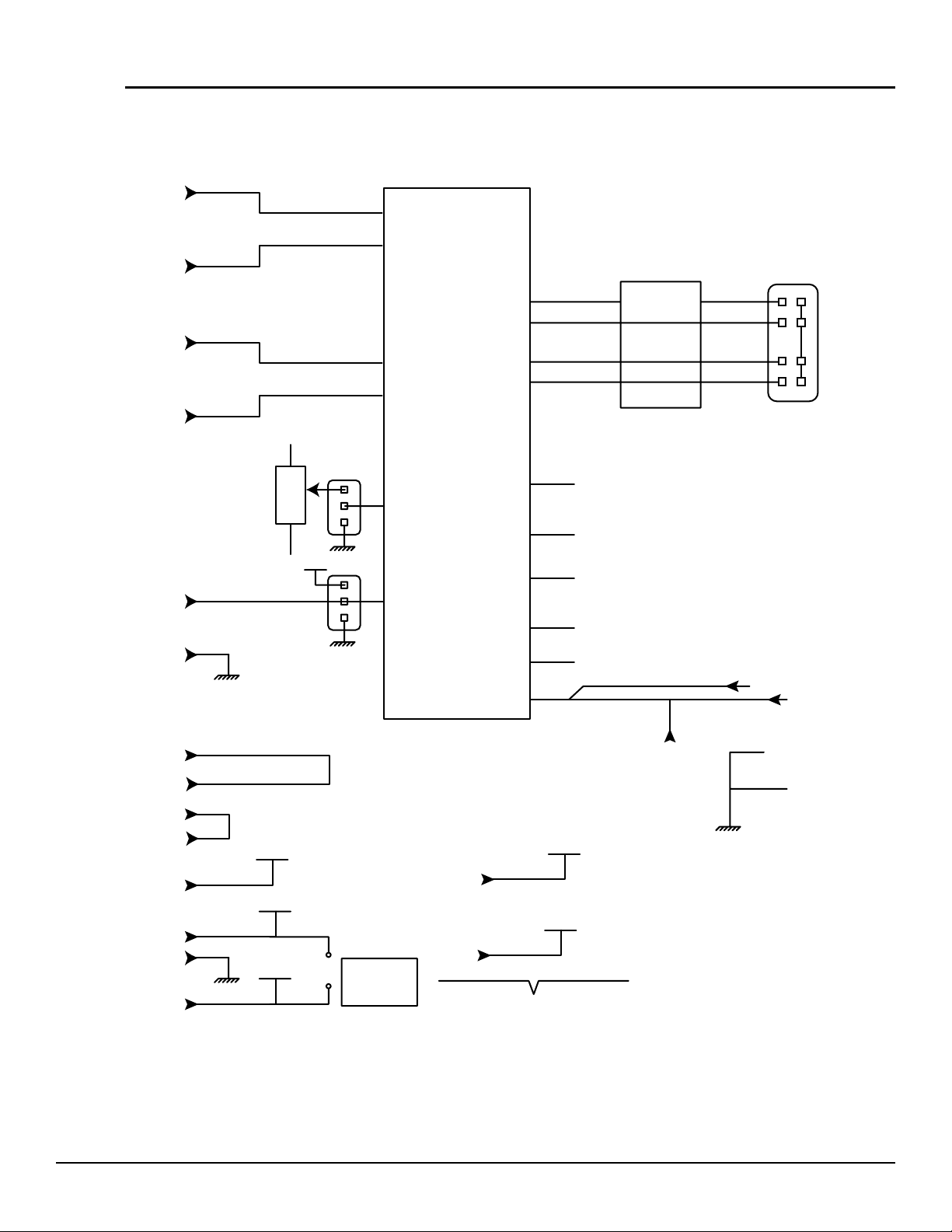

2.5 Board

Implementation

Surface-mount resistors and chip capacitors allow the closest possible connections to

the device pins, for microstrip line back termination and bypassing.

Connecting the positive supply pads:

– The positive supply pads denoted VCC:

The corresponding VCC pad numbers are 19, 21, 23, 30, 39, 40.

Each VCC power supply pad is decoupled as closely to the device as possible

by a 10 nF and 100 pF chip capacitor.

The VCC supply pads are connected to the back side VCC plane of the CEB.

– The positive digital supply pads are denoted VPLUSD (0V or 2.4V).

The corresponding VPLUSD pad numbers are 1, 11.

Each VPLUSD power supply pad is decoupled very close to the device by a

10 nF and 100 pF chip capacitor.

The VPLUSD supply pads are connected to the back side VPLUSD plane of the

evaluation board.

Connecting the negative supply pads:

– The TS8308500 has separate analog and digital -5V supplies:

The negative analog supply pads are denoted VEE.

The VEE corresponding pad numbers are 22, 29, 31.

The negative digital supply pad is denoted DVEE.

The DVEE corresponding pad number is pad 6.

The DVEE supply pad is dedicated to the digital output buffers only.

Each VEE and DVEE power supply pad is decoupled as closely as possible

near the device by a 10 nF and 100 pF chip capacitor.

–TheV

EE and DVEE supply pads are respectively connected to the backside

layer 7 VEE and VEED supply planes.

Ground pads connections:

– The analog ground pads are denoted GND.

The corresponding GND pad numbers are 20, 26, 28, 33, 35, 37.