S1V30080 Series Evaluation Board User’s Guide EPSON i

(Rev. 1.00)

Table of Contents

1. Introduction .................................................................................................................. 1

1.1 Overview ......................................................................................................................................1

1.2 Cinderella board series configuration.......................................................................................2

1.3 User guide overview....................................................................................................................2

2. Before Starting.............................................................................................................. 3

2.1 Items provided.............................................................................................................................3

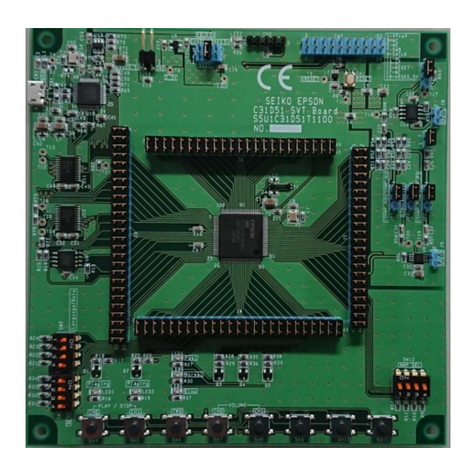

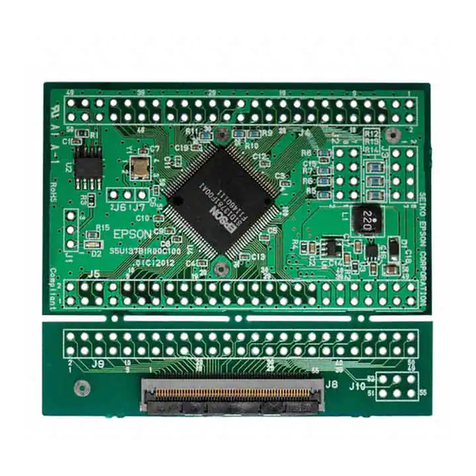

2.2 Cinderella (S1V30080 voice LSI evaluation board)...................................................................4

2.2.1 Part names and functions ....................................................................................................... 4

2.2.2 Cinderella block diagram....................................................................................................... 10

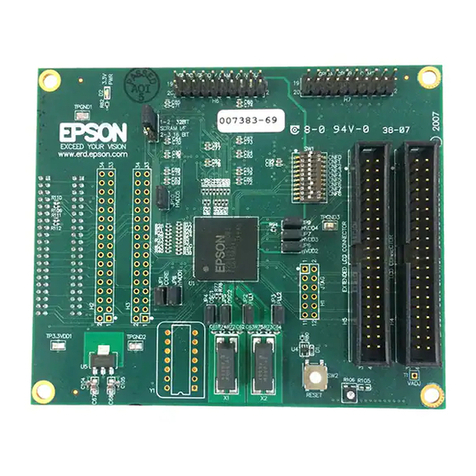

2.3 CASTLE board........................................................................................................................... 11

2.3.1 CASTLE Part names and functions....................................................................................... 11

2.3.2 CASTLE block diagram......................................................................................................... 16

2.4 Cinderella and CASTLE connection ........................................................................................17

3. Usage Instructions..................................................................................................... 18

3.1 Writing data to Cinderella board ..............................................................................................18

3.1.1 Data writing flowchart............................................................................................................ 19

3.1.2 Cinderella board data writing micro SD card......................................................................... 21

3.2 Cinderella board standalone demo..........................................................................................22

3.2.1 Standalone mode 1 control.................................................................................................... 23

3.2.2 Standalone mode 2 control.................................................................................................... 24

3.3 Connecting to an external host CPU .......................................................................................25

4. Usage Precautions..................................................................................................... 27

4.1 DIP switch definitions ...............................................................................................................27

4.2 Voice output pin precautions ...................................................................................................27

4.3 External power supply precautions.........................................................................................28

4.4 PLD and external flash memory power supply selector jumper pin J6................................ 28

4.5 Micro SD card precautions.......................................................................................................28

5. Board Circuit Diagram ............................................................................................... 29

Revision History............................................................................................................. 35