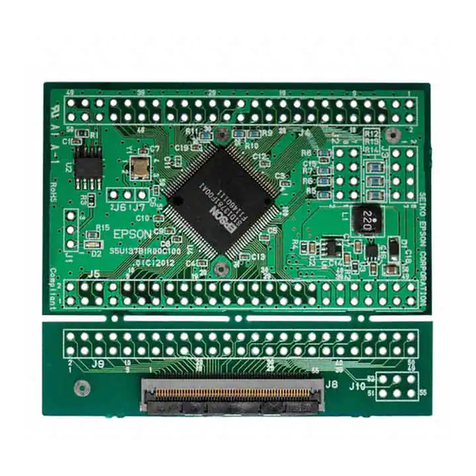

S5U13A04B00C Rev 1.0 Evaluation Board Seiko Epson Corporation 3

Rev. 3.1

Table of Contents

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3 Installation and Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.1 Configuration DIP Switches . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.2 Configuration Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

4 CPU Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4.1 CPU Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . 12

4.2 CPU Bus Connector Pin Mapping . . . . . . . . . . . . . . . . . . . . . . 13

5 LCD Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

6 Technical Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

6.1 PCI Bus Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

6.2 Direct Host Bus Interface Support . . . . . . . . . . . . . . . . . . . . . . 18

6.3 S1D13A04 Embedded Memory . . . . . . . . . . . . . . . . . . . . . . . 18

6.4 Adjustable LCD Panel Negative Power Supply . . . . . . . . . . . . . . . . . 18

6.5 Adjustable LCD Panel Positive Power Supply . . . . . . . . . . . . . . . . . . 19

6.6 Software Adjustable LCD Backlight Intensity Support Using PWM . . . . . . . . . 19

6.7 LCD Panel Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

6.7.1 Direct LCD Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

6.7.2 Extended LCD Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

6.8 USB Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

6.8.1 USB IRQ Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

7 Clock Synthesizer and Clock Options . . . . . . . . . . . . . . . . . . . . . . . . 21

7.1 Clock Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

8 Parts List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

9 Schematics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

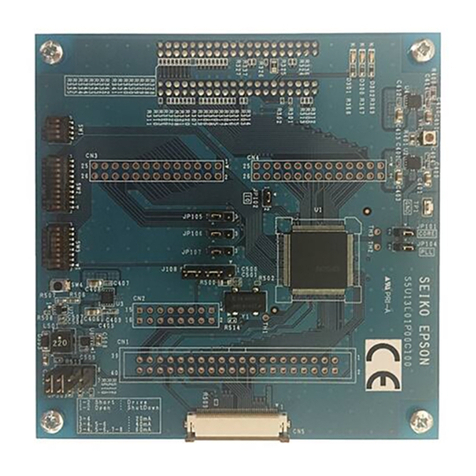

10 Board Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

11 Change Record . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

12 Sales and Technical Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32