Epson Research and Development Page 3

Vancouver Design Center

S5U13513P00C100 Evaluation Board User Manual S1D13513

Issue Date: 2010/09/06 X78A-G-003-01

Revision 1.1

Table of Contents

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3 Installation and Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.1 Configuration DIP Switch . . . . . . . . . . . . . . . . . . . . . . . . . . .7

3.2 Configuration Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4 Technical Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

4.1 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

4.1.1 Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

4.1.2 Voltage Regulators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

4.1.3 S1D13513 Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

4.2 Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.3 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.4 Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

4.4.1 Connecting to the Epson S5U13U00P00C100 USB Adapter Board . . . . . . . . . 15

4.4.2 Connecting to the Epson PC Card Extender Board . . . . . . . . . . . . . . . . . . 15

4.4.3 Direct Host Bus Interface Support . . . . . . . . . . . . . . . . . . . . . . . . . . 16

4.5 LCD Panel Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

4.6 Camera Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4.7 YUV Output for TV Display . . . . . . . . . . . . . . . . . . . . . . . . 19

4.8 Keypad Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.9 PWM Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.10 GPIO Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.11 JTAG Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5 Parts List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

6 Schematic Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

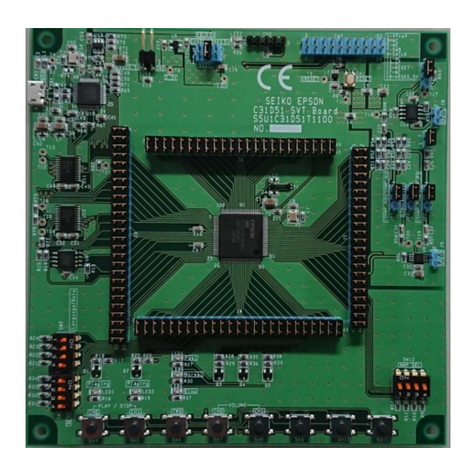

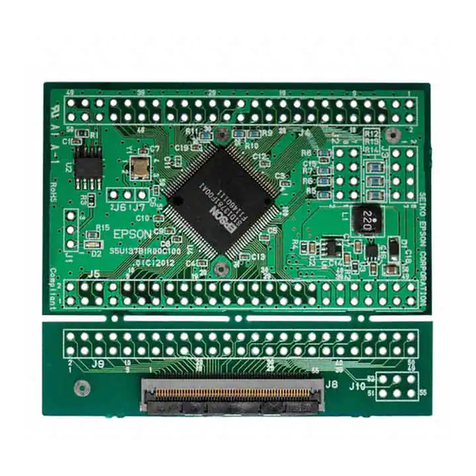

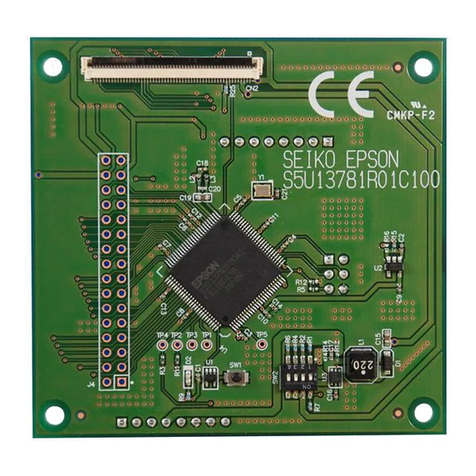

7 S5U13513P00C100 Board Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

8 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

8.1 Documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

8.2 Document Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

9 Technical Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

9.1 EPSON Display Controllers (S1D13513) . . . . . . . . . . . . . . . . . . . . 31

9.2 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . 31