Introduction 2/66

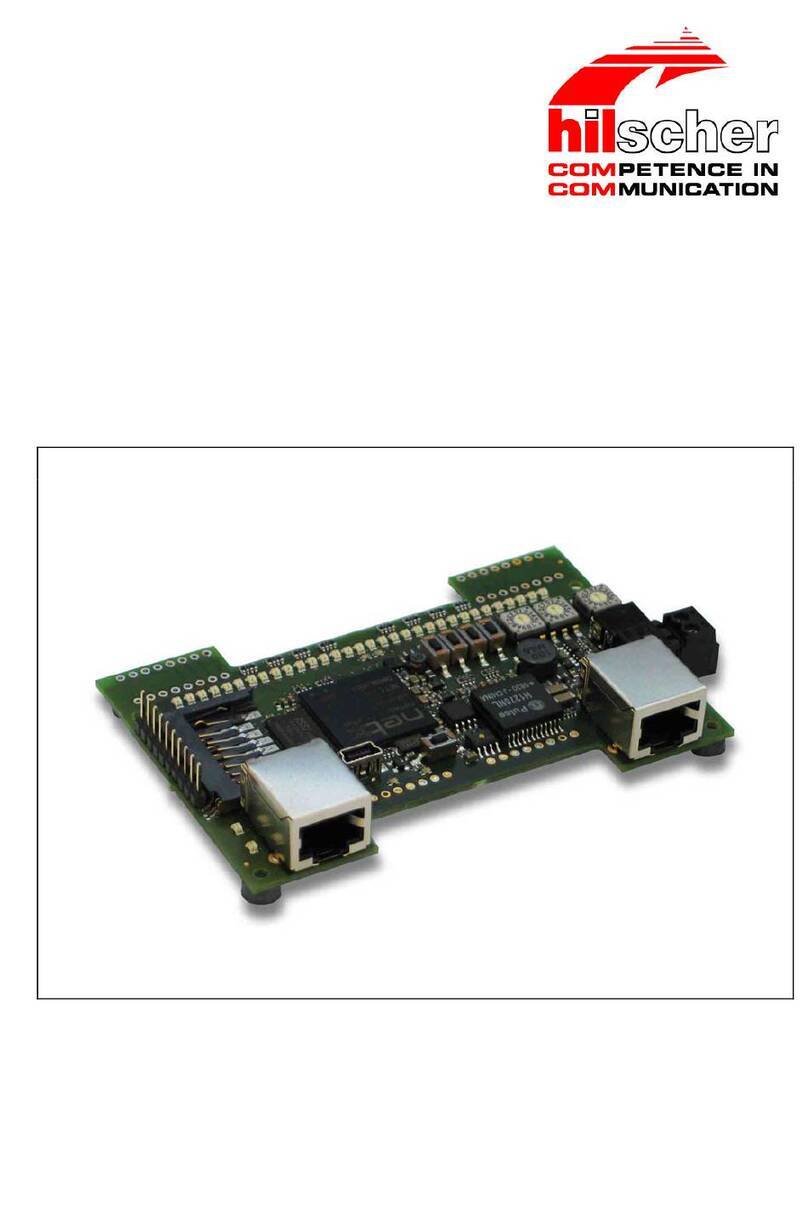

netX 90 | Design-In Guide

DOC180501DG02EN | Revision 2 | English | 2018-09 | Preliminary | Public © Hilscher, 2018

Table of contents

1Introduction.............................................................................................................................................4

1.1 About this document ......................................................................................................................4

1.2 List of revisions...............................................................................................................................5

1.3 References to documents ..............................................................................................................5

2Basic concepts.......................................................................................................................................6

2.1 netX 90 – introduction ....................................................................................................................6

2.2 netX 90 – use cases.......................................................................................................................7

2.3 Design checklist .............................................................................................................................8

3Basic circuits........................................................................................................................................10

3.1 Power supply................................................................................................................................10

3.1.1 Integrated core voltage regulator..................................................................................................... 10

3.2 Brown-Out Detector (BOD)..........................................................................................................11

3.3 Power-on reset and reset in.........................................................................................................12

3.4 System clock................................................................................................................................13

3.5 Boot sequence .............................................................................................................................14

3.5.1 Configuration pins ........................................................................................................................... 14

3.5.1.1 Console mode ................................................................................................................ 15

3.5.1.2 Alterative boot mode....................................................................................................... 15

3.5.1.3 System RDY/RUN LED .................................................................................................. 16

3.6 External memory..........................................................................................................................17

3.6.1 Serial memory interface................................................................................................................... 18

3.6.1.1 QSPI Flash..................................................................................................................... 18

3.6.2 Parallel memory interface................................................................................................................ 19

3.6.2.1 SDRAM........................................................................................................................... 19

3.7 Host interface...............................................................................................................................21

3.7.1 Dual-port memory............................................................................................................................ 22

3.7.1.1 8/16-bit data width and dual-port memory size............................................................... 22

3.7.1.2 Control lines.................................................................................................................... 22

3.7.1.3 Non-multiplexed mode.................................................................................................... 23

3.7.1.4 Multiplexed mode ........................................................................................................... 26

3.7.1.5 Ready/Busy signal.......................................................................................................... 27

3.7.2 Serial port memory (SPI/QSPI access to DPM) .............................................................................. 28

3.8 PIO signals...................................................................................................................................29

3.8.1 External pull-ups/pull-downs, unused signals.................................................................................. 29

3.9 Multiplexed IO matrix (MMIO)......................................................................................................30

3.10 General purpose IOs....................................................................................................................32

3.11 Serial interfaces ...........................................................................................................................33

3.11.1 UARTs............................................................................................................................................. 33

3.11.2 SPI................................................................................................................................................... 34

3.11.3 SQI.................................................................................................................................................. 34

3.11.4 I2C................................................................................................................................................... 35

3.11.5 CAN................................................................................................................................................. 35

3.12 IO-Link..........................................................................................................................................36

3.13 Motion control...............................................................................................................................36

3.14 Analog to digital converter............................................................................................................37

3.15 Encoder interfaces .......................................................................................................................37

3.16 Fieldbus interfaces.......................................................................................................................38

3.16.1 CANopen interface.......................................................................................................................... 38

3.16.2 CC-Link interface............................................................................................................................. 39

3.16.3 DeviceNet interface......................................................................................................................... 39

3.16.4 PROFIBUS interface ....................................................................................................................... 40

3.16.5 Fieldbus status LEDs....................................................................................................................... 40

3.17 Real-time Ethernet (RTE) interface..............................................................................................41

3.17.1 Twisted pair..................................................................................................................................... 41

3.17.2 Unused Ethernet PHYs ................................................................................................................... 44

3.17.3 Ethernet status LEDs....................................................................................................................... 45

3.17.3.1 Ethernet communication status LEDs............................................................................. 45

3.17.3.2 Real-time Ethernet protocol status LEDs........................................................................ 46

3.17.4 Real-Time Ethernet synchronization signals ................................................................................... 47

4Debug and test interfaces ...................................................................................................................48