Contents

Aboutthisguide .......................... 7

Intendedaudience...................................... 7

Relateddocumentation.................................... 7

Documentconventionsandsymbols .............................. 7

HPtechnicalsupport..................................... 8

Subscriptionservice ................................... 9

Helpfulwebsites .................................... 9

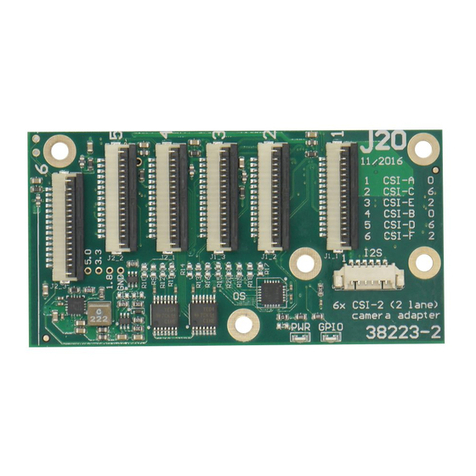

1HBAfeatures........................... 11

Performance specifications .................................. 11

Environmental specifications................................. 12

Physical specifications ................................... 13

Media specifications.................................... 13

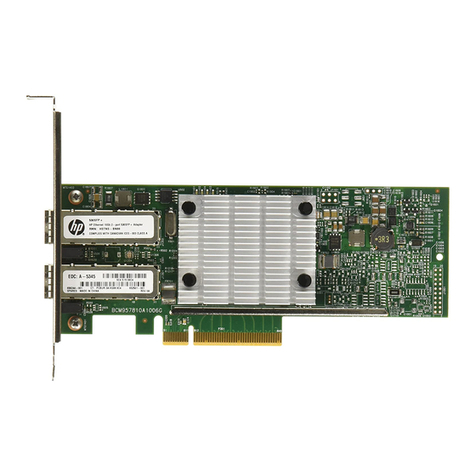

2 Installing the HBAs . . ...................... 15

Installationprerequisites .................................. 15

HBALEDs ........................................ 15

Recordingreferencenumbers ................................ 16

InstallingtheHBA ..................................... 16

3InstallingtheLinuxdriver..................... 19

Prerequisites ....................................... 19

InstallingtheLinuxdriver .................................. 19

4InstallingtheWindowsdrivers................... 21

Prerequisites ....................................... 21

InstallingdriversusingtheSmartComponent.......................... 21

5Troubleshooting . ........................ 23

POSTconditionsandresults................................. 23

UsingtheEventViewer................................... 23

Viewingtheeventlog ................................... 24

Windowsminiporteventlogcodes.............................. 24

Linuxdriverevents..................................... 24

Settingthejumpers..................................... 24

6Regulatorycomplianceandsafety................. 27

Laserdevice ....................................... 27

Lasersafetywarning.................................... 27

Certification and classificationinformation........................... 27

Laserproductlabel..................................... 27

Internationalnoticesandstatements ............................. 28

Canadiannotice(avisCanadien) .............................. 28

ClassAequipment................................... 28

EuropeanUnionnotice................................... 28

BSMInotice........................................ 29

Japanese notice . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

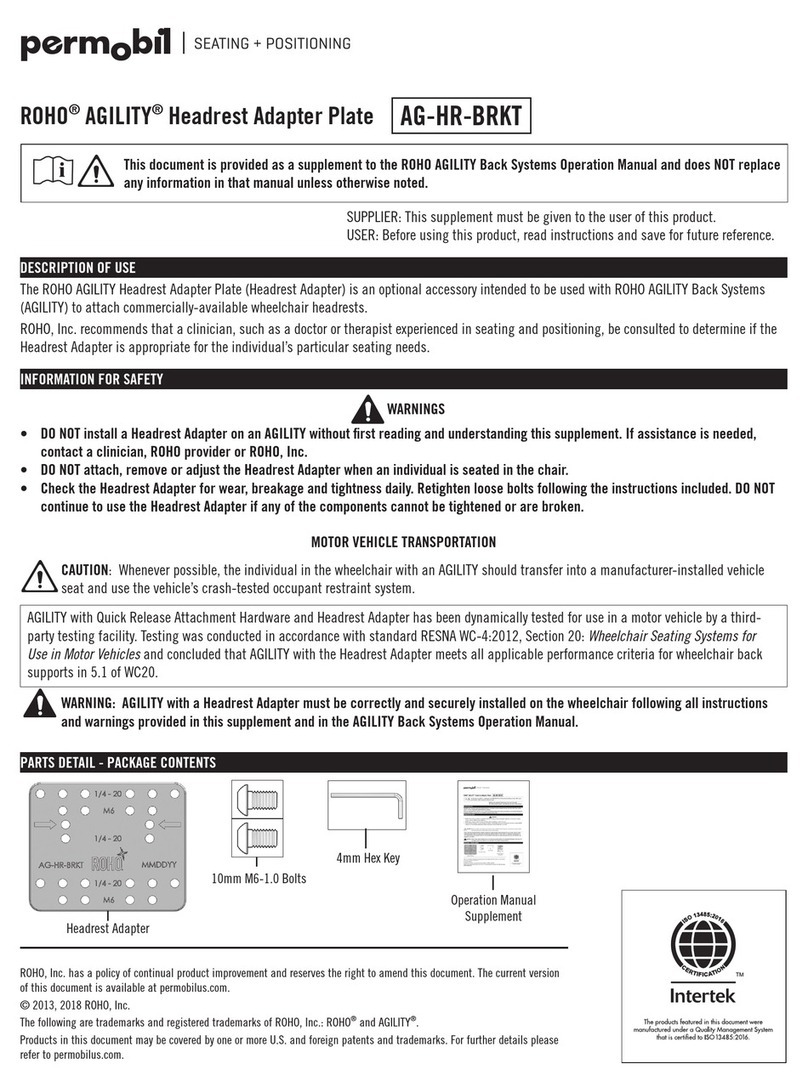

A8002A PCI-e single-port 4Gb FC adapter and A8003A PCI-e dual-port 4Gb FC adapter for Linux and

Windows systems installation guide 3