Contents

vi DRAFT

Draft: Status: Author: Reviewer:

DRAFT First Malcolm SHUTE Saxo TRM team

3 Interface Devices and Mass-Storage Drives

S3 Trio 64V2 Graphics Controller Chip. . . . . . . . . . . . . . . . . . . . . . . . 34

Video Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Available Video Resolutions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Audio Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Mass-Storage Drives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Hard Disk Drives. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Flexible Disk Drives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

CD-ROM Drives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

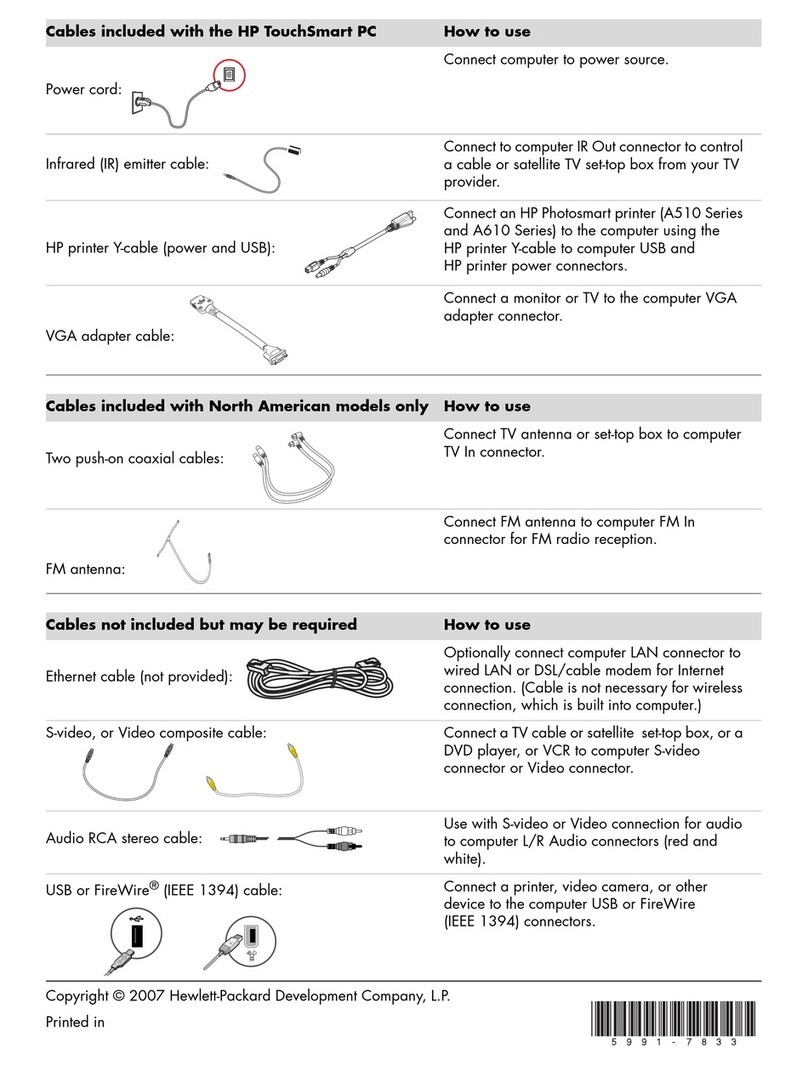

Connectors and Sockets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

4 Summary of the HP/Phoenix BIOS

HP/Phoenix BIOS Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Setup Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Main Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Advanced Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Security Menu. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Power Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Power Saving and Ergonometry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Desktop Management Interface (DMI) . . . . . . . . . . . . . . . . . . . . . . . . . . 52

HP Lock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Power-On from Space-Bar . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

HP Off and Soft Power Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Remote Power-On (RPO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Advanced Power Management (APM) . . . . . . . . . . . . . . . . . . . . . . . . . . 55

BIOS Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

1book.bk : 1book.toc Page vi Thursday, August 21, 1997 9:43 AM