Model 1332A GeneralInformation

SECTION

I

GENERAL INFORMATION

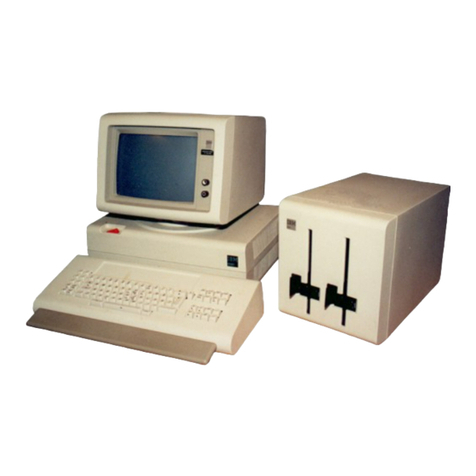

1-2. The Hewlett-Packard Model 1332A is a cathode-

ray tube display that is capable of meeting a wide

variety of OEM medical and electronic instrument dis-

play needs. Thecathode-raytubehastheresolution and

picture quality required for medical diagnostic systems

plus an extremely bright display required for differ-

entiating between many gray shades.

1-3. This manual contains installation and operating

instructions, as well as maintenance information for

the 1332A. Instrument specifications and procedures

for verifying proper operation areincluded. Procedures

are also included for adjusting the instrument to its

performance specifications. Schematic diagrams, the

theory of operation, and troubleshooting information

are provided for use in maintaining the instrument.

1-4. This section of the manual contains the per-

formance specifications for the 1332A, and a list of

options available. It also lists the accessories supplied

with the 1332Aandother accessories thatareavailable.

Instrument and manual identification information are

also included.

1-5. SPECIFICATIONS.

1-6. Table 1-1is a complete list of the 1332A critical

specifications that are controlled by tolerances. Table

1-2 contains general information that describes

operating characteristics of the 1332A.

1-7. Any change in the specifications due to'manu-

facturing, design, or traceability to the U.S. National

Bureau of Standards will be listed on a manual change

sheet included with this manual. The manual and

manualchangesheetsupersedeallpreviousinformation

concerning specifications of the 1332A.

1-8. ACCESSORIES SUPPLIED.

1-9. The following accessories are supplied with the

1332A:

One Blue Contrast Filter, HP Part No. 01332-

02706.

One 0.375A Fuse for 220/240-Vac operation, HP

Part No. 2110-0063.

One2.3m (7.5ft)linecord,HPPartNo. 8120-1538.

1-10. ACCESSORIES AVAILABLE.

1-11. The following accessories are available for the

1332A:

Model 10380A OEM Horizontal Frame Kit.

Model 10381A Rack Mount Hardware Kit for

Model 10380A.

Model 10382A Bench Hardware Kit for Model

10380A.

Model 10383A Rack Mount Adapter.

Model 10384ARack Mount Kit forTwo Displays.

Model 10385ARack Mount Kit forTwo Displays.

Model 10386A OEM Vertical Frame.

BNC Shorting Caps,

HP

Part No. 1250-0645.

Camera Model 197A Option 006.

Model 10488A Input Signal Cable.

1-13. Standard options are modifications installed on

HP instruments at the factory and are available on

request. Table 1-3lists available options for the 1332A.

For information on field-installable options, refer to

Application Note 199,"Small Screen Displays, Medical

Diagnostic System Application and Interfacing."

1-14. INSTRUMENT AND MANUAL IDENTI-

FICATION.

1-15. Instrument identification by serial number is

located on the rear panel. Hewlett-Packard uses a two-

sectionserialnumber consisting of four-digitprefix and

a five-digitsuffix separated by a letter designating the

country in which the instrument was manufactured.

(A

=

U.S.A; G

=

West Germany;

J

=

Japan;

U

=

United

Kingdom.)

1-16. This manual applies to instruments with a

serial number as shown on the title page. If changes

have been made in the instrument since this manual

was printed, a "Manual Changesr' supplement sup-

plied with the manual will define these changes. Be

sure to record these changes in your manual. Back-

dating information in Section VII adapts the manual

to instrument with serial numbers lower than that

shown on title page. Part Numbers for the manual

and the microfiche copy of the manual arealso shown

on the title page.

Scans by ArtekMedia © 2008