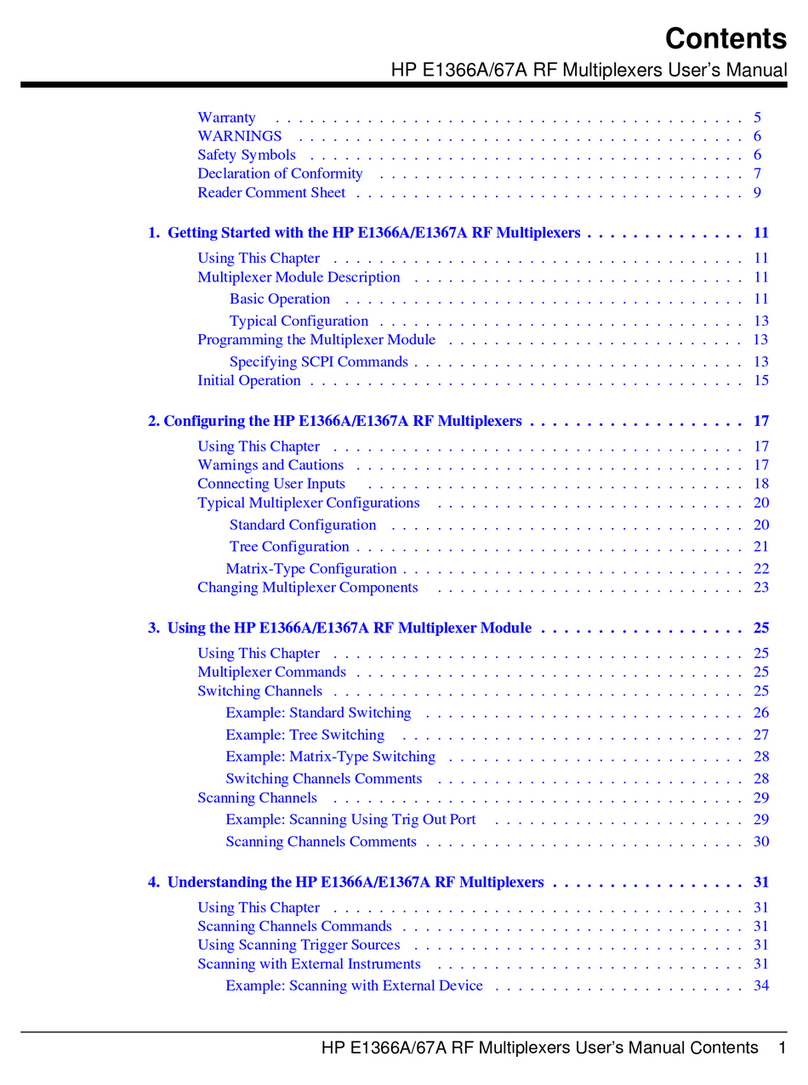

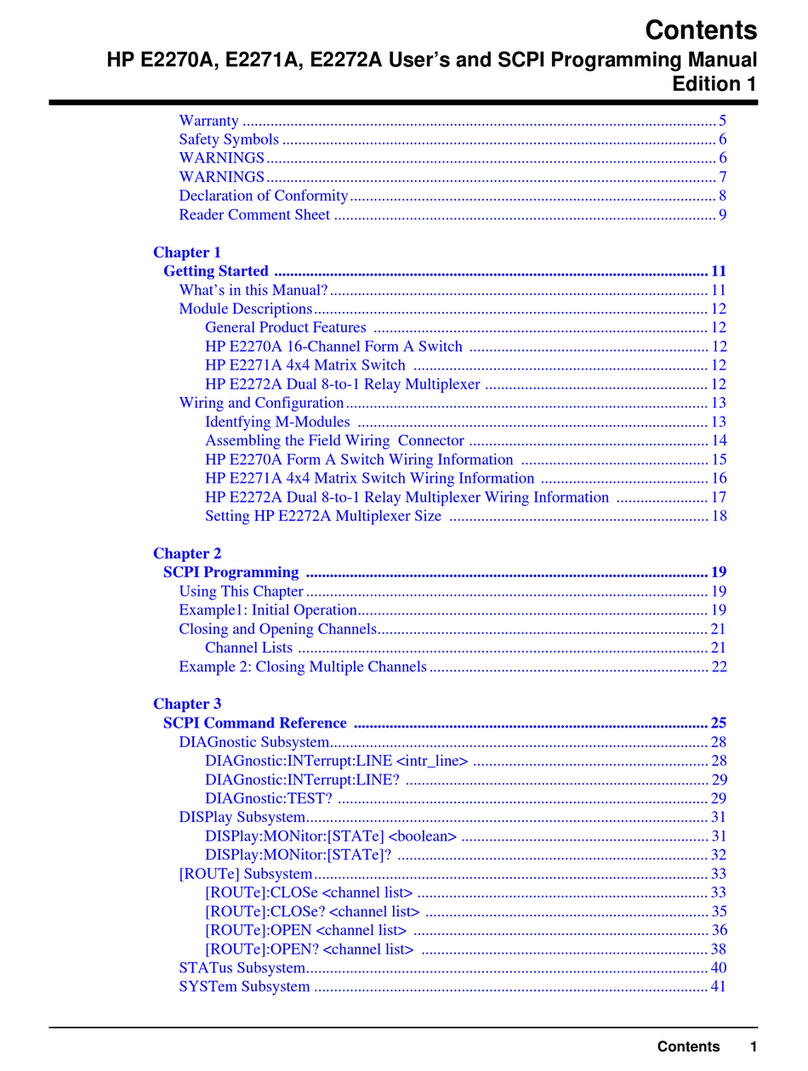

CONTENTS

(Cont.)

Priority

Interrupt

Structure

...........................................

3-27

Wait

State

Circuits

for

Interrupt

Ack

..................................

3-27

Diagnostic

Hood

for

External

Loop

Back

3-28

Section

IV

PROGRAM1ING

MUX

PROGRAf'tT1ABLE

FEATURES

.................................................

4-1

Transactions

4-2

Connect

Logical

Channel

Reguest

Format

....................................

4-2

Capabi

lit

ies

4-3

Receive

Character

Processing

............................................

4-3

Receive

Error

Conditions

4-5

Signal

Character

........................................................

4-5

Edit

Mode

4-5

Bac

k

space

.............................................................

4-5

Line

Deletion

4-6

Software

Handshake

with

the

Device

...........................

~

..........

4-6

Host

ENQ/ACK

Handshake

4-7

Device

X-ON/X-OFF

Handshake

...........................................

4-7

Host

X-ON/X-OFF

Handshake

4-8

Si

ngle

Text

Termi

nat

ion

.................................................

4-8

End-On-Count Text

Termination

4-8

Aler t 1

Mo

de.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Type Ahead and Echoing

4-9

Receiving

Transparent

or

Binary

Data

...................................

4-10

Read

Reguest

Length 4-10

Host

Initiated

Text

Termination

........................................

4-11

Transmit

Character

Processing

4-11

Automatic

Output

Separators

Appendage

..................................

4-12

Transmitting

Transparent

or

Binary

Data

4-12

Buffer

Flushing

4-12

Prograrrmi

ng

the

Receiver

and

Transmi

tter

...................................

4-12

Parity

in

Transmitted

or

Received

data

4-13

Break

Detection

4-13

Handshake Timer

...................................................•......

4-14

Additional

Options

4-14

Error

Handling

..................•...............................•......

4-14

Quoting

Character

Mode

Option

4-17

Condi

tional

Output

Separators

Appendage

................................

4-17

Speed

Sense

Mode

4-17

Asynchronous Events

......................................................

4-17

Solicited

Events

4-18

Diagnostics

..............................................................

4-18

Connect

Logical

Channel

Reguest

Definitions

4-19

Read

Device

Data,

Request Code = 1

.....................................

4-19

Write

Device

Data,

Reguest

Code = 2 4-20

Read Card

Information,

Request

Code = 4

................................

4-20

Subfunctions

0

through

33 4-20

Subfunct

ion

249 -Read

Data

Status

...................................

4-21

Subfunction

250. Get Card

RAM

4-21

Subfunction

254. Get Card

Status

....................................

4-21

Write

Card

Configuration,

Reguest

Code = 5 4-22

Subfunction

0

........................................................

4-23

Subfunction

................................................................

4-25

1.

Configure

Read

Option

4-25

2.

End-On-Cou

nt

Length

..........................

,;

...................

4-26

3.

Alert

1 Read

Mode

4-26

IV