Intel MCS48 User manual

Other Intel Computer Hardware manuals

Intel

Intel Pentium OverDrive User manual

Intel

Intel Core i7-980X Operating and safety instructions

Intel

Intel CORE 2 DUO PROCESSOR E8000 - Reference guide

Intel

Intel Xeon X5570 User manual

Intel

Intel AXXROMBSASMR Installation manual

Intel

Intel SRCZCR - RAID Controller Storage User manual

Intel

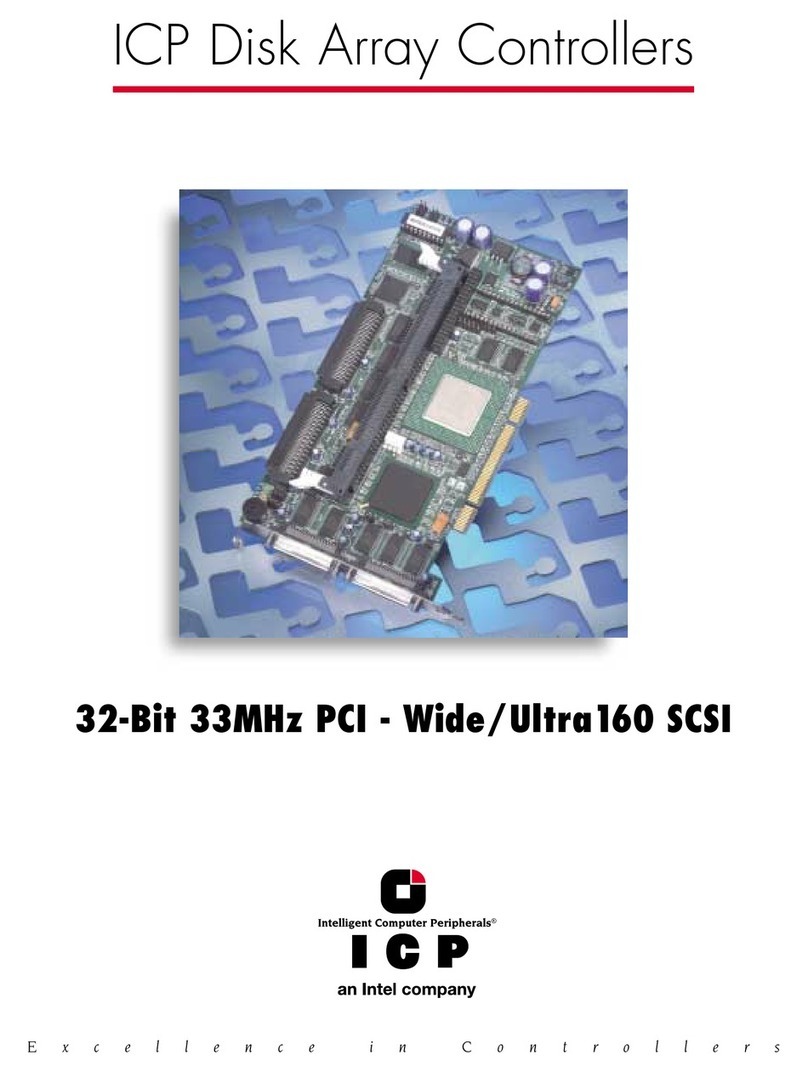

Intel GDT6113RS User manual

Intel

Intel core i5 X series User manual

Intel

Intel VC820 - Desktop Board Motherboard Guide

Intel

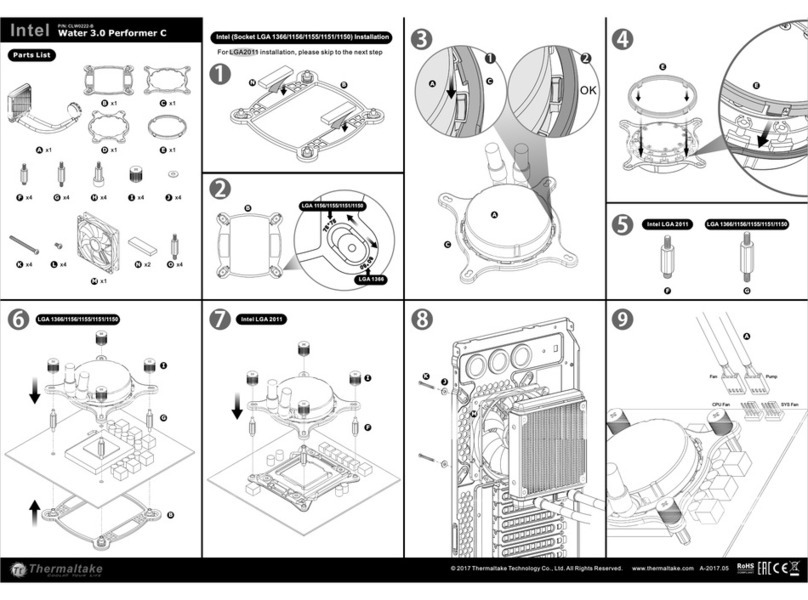

Intel Water 3.0 Performer C User manual

Intel

Intel BX80637I53570K User manual

Intel

Intel E1400 - Celeron 2.0GHz 800MHz 512KB Socket 775 Dual-Core... Guide

Intel

Intel Core i7 Extreme Edition User manual

Intel

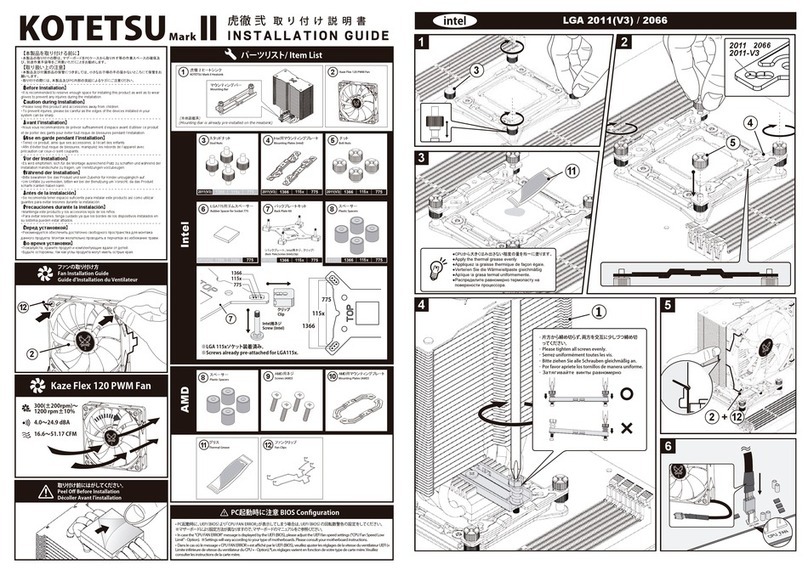

Intel KOTETSU Mark II User manual

Intel

Intel RES2SV240 Installation manual

Intel

Intel AXXRMFBU4 User manual

Intel

Intel ETHEREXPRESS PRO/100 User manual

Intel

Intel Xeon Processor E5-2600 Mounting instructions

Intel

Intel Atom N2800 User manual

Intel

Intel Xeon Phi Processor x200 Guide

Popular Computer Hardware manuals by other brands

EMC2

EMC2 VNX Series Hardware Information Guide

Panasonic

Panasonic DV0PM20105 Operation manual

Mitsubishi Electric

Mitsubishi Electric Q81BD-J61BT11 user manual

Gigabyte

Gigabyte B660M DS3H AX DDR4 user manual

Raidon

Raidon iT2300 Quick installation guide

National Instruments

National Instruments PXI-8186 user manual