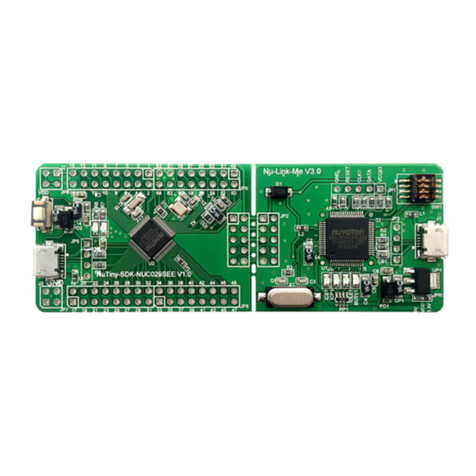

NuMicro® NUC029LEE/NUC029SEE

32-bit Arm®Cortex®-M0 Microcontroller

Aug, 2018 Page 9of 497 Rev 1.00

NUMICRO®NUC029LEE/NUC029SEE TECHNICAL REFERENCE MANUAL

Figure 6.13-16 UA_BAUD Update Sequence in Automatic Resynchronization Mode when

LINS_DUM_EN (UA_LIN_CTL[3])= 0................................................................................... 355

Figure 6.13-17 RS-485 RTS Driving Level in Auto Direction Mode............................................. 358

Figure 6.13-18 RS-485 RTS Driving Level with Software Control.............................................. 358

Figure 6.13-19 Structure of RS-485 Frame ................................................................................. 359

Figure 6.14-1 I2C Controller Block Diagram................................................................................. 390

Figure 6.14-2 I2C Bus Timing....................................................................................................... 391

Figure 6.14-3 I2C Protocol........................................................................................................... 391

Figure 6.14-4 START and STOP Conditions............................................................................... 392

Figure 6.14-5 Bit Transfer on the I2C Bus.................................................................................... 393

Figure 6.14-6 Acknowledge on the I2C Bus................................................................................. 393

Figure 6.14-7 Master Transmits Data to Slave............................................................................ 393

Figure 6.14-8 Master Reads Data from Slave ............................................................................. 394

Figure 6.14-9 Control I2C Bus according to Current I2C Status................................................... 394

Figure 6.14-10 Master Transmitter Mode Control Flow............................................................... 395

Figure 6.14-11 Master Receiver Mode Control Flow................................................................... 396

Figure 6.14-12 Save Mode Control Flow..................................................................................... 397

Figure 6.14-13 GC Mode ............................................................................................................. 398

Figure 6.14-14 Arbitration Lost..................................................................................................... 399

Figure 6.14-15 I2C Data Shifting Direction................................................................................... 400

Figure 6.14-16 I2C Time-out Count Block Diagram ..................................................................... 402

Figure 6.14-17 EEPROM Random Read..................................................................................... 403

Figure 6.14-18 Protocol of EEPROM Random Read .................................................................. 404

Figure 6.15-1 SPI Block Diagram................................................................................................. 417

Figure 6.15-2 SPI Master Mode Application Block Diagram........................................................ 418

Figure 6.15-3 SPI Slave Mode Application Block Diagram.......................................................... 418

Figure 6.15-4 32-Bit in One Transaction...................................................................................... 419

Figure 6.15-5 Variable Bus Clock Frequency.............................................................................. 421

Figure 6.15-6 Byte Reorder Function........................................................................................... 421

Figure 6.15-7 Timing Waveform for Byte Suspend...................................................................... 422

Figure 6.15-8 Bit Sequence of Dual Output Mode....................................................................... 423

Figure 6.15-9 Bit Sequence of Dual Input Mode.......................................................................... 423

Figure 6.15-10 FIFO Mode Block Diagram.................................................................................. 424

Figure 6.15-11 SPI Timing in Master Mode ................................................................................. 426

Figure 6.15-12 SPI Timing in Master Mode (Alternate Phase of SPI Bus Clock)........................ 426

Figure 6.15-13 SPI Timing in Slave Mode ................................................................................... 427

Figure 6.15-14 SPI Timing in Slave Mode (Alternate Phase of SPI Bus Clock).......................... 427