NXP Semiconductors UM11650

KIT-TPLSNIFEVB tool

only one differential end available for connection to the TPL sniffer, there is no difference

between the TPL_IN and TPL_OUT connectors, as long as the polarity is respected.

As a rule, if a branch is created from the original TPL bus, its length should be as short

as possible.

Note: The two TPL interface connectors are named J1 and J2 in the schematic diagram.

Figure 5. TPL bus connectors

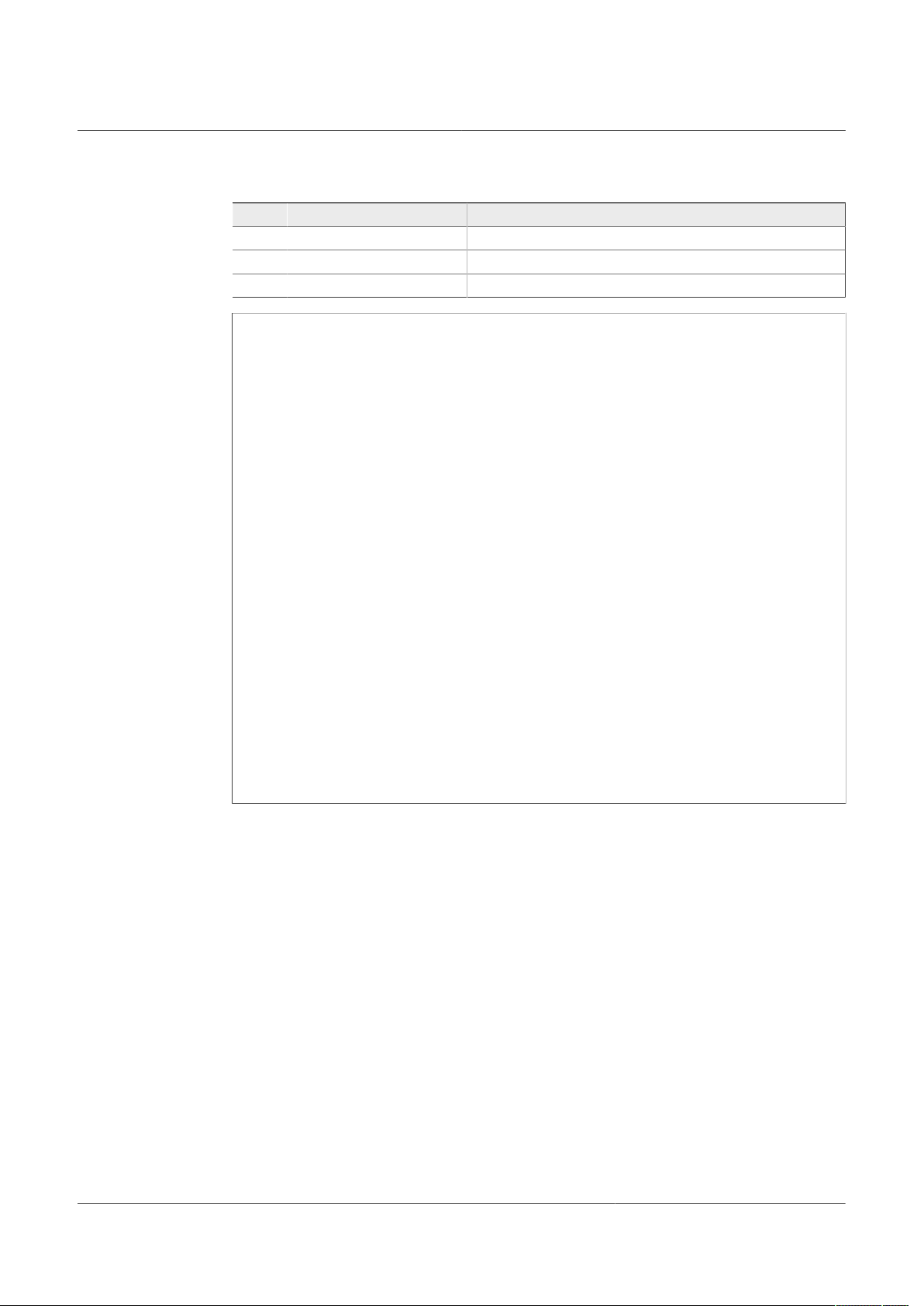

5.1.1 Optional TPL bus loading

The TPL sniffer is designed to add minimal load to the TPL bus by default. Therefore, it

does not add any termination impedance and the differential load seen from the bus is

that of an input impedance of the MC33664 reflected on the high voltage side by the 1:1

ratio T1 isolation transformer.

In case an interface other than the default one is desired, some settings are possible on

the PCB:

•The two jumpers JP1 and JP2 located on the bottom side, should be closed (with a

drop of solder) in case a standard 150 Ω termination is desired.

•Additional component footprints are available on the top side of the PCB to

accommodate different loads on the TPL bus interface. These are R13 (default DNP)

and R14 and R15 (default 0 Ω).

Note: If the board must be modified and then powered without housing, proceed with

caution.

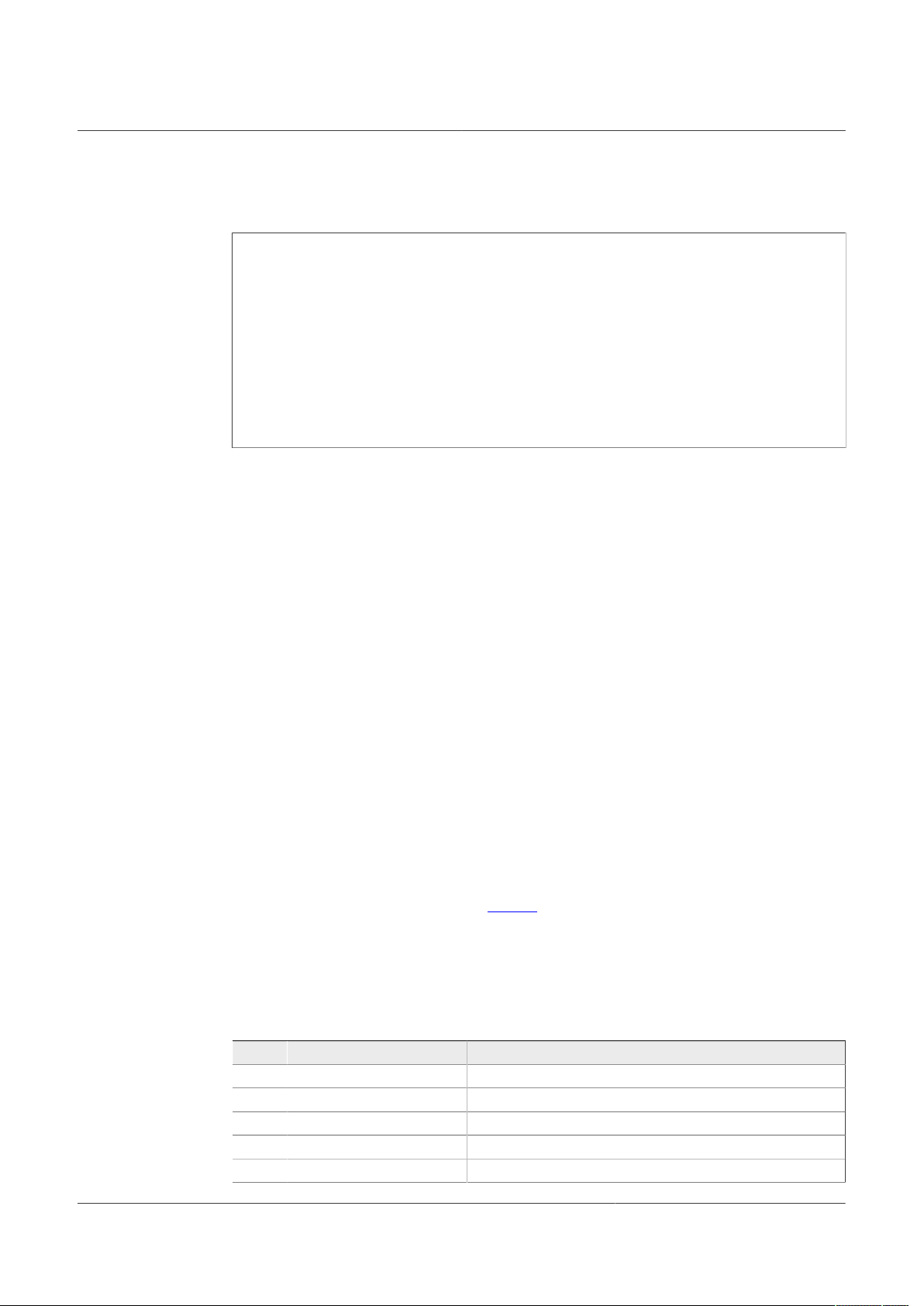

5.2 Power and data connections

The side of the case opposite the TPL connectors has all the other available connectors

of the TPL sniffer.

•The GND banana plug: used to connect, if necessary, the GND of the TPL sniffer to

another potential. It is labeled J5 in the schematics.

In some cases of use, the whole system including, for example, the TPL sniffer, the

power supply, the logic analyzer and the associated PC, could be an electrically

floating block. This connector allows, if desired, the ground potential of the system (for

example, the TPL sniffer and anything else that has its ground connected to the TPL

sniffer ground) to be set to any other convenient potential, that is, the protective earth

or the vehicle chassis ground (KL31).

•The data-out 8-pin connector: buffered SPI signals to be routed to the logic analyzer. It

is labeled J3 in the schematics. See Section 5.2.1 "Connecting to the logic analyzer" for

more details.

•The power-on LED indicator

UM11650 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2021. All rights reserved.

User manual Rev. 1 — 4 August 2021

7 / 14