NXP Semiconductors UM11603

RDGD31603PHSEVM three-phase inverter reference design

1 Introduction

This document is the user guide for the RDGD31603PHSEVM reference design.

This document is intended for the engineers involved in the evaluation, design,

implementation, and validation of single-channel gate driver for IGBT/SiC, GD3160.

The scope of this document is to provide the user with information to evaluate the

single channel gate driver for IGBT/SiC, GD3160. This document covers connecting the

hardware, installing the software and tools, configuring the environment and using the kit.

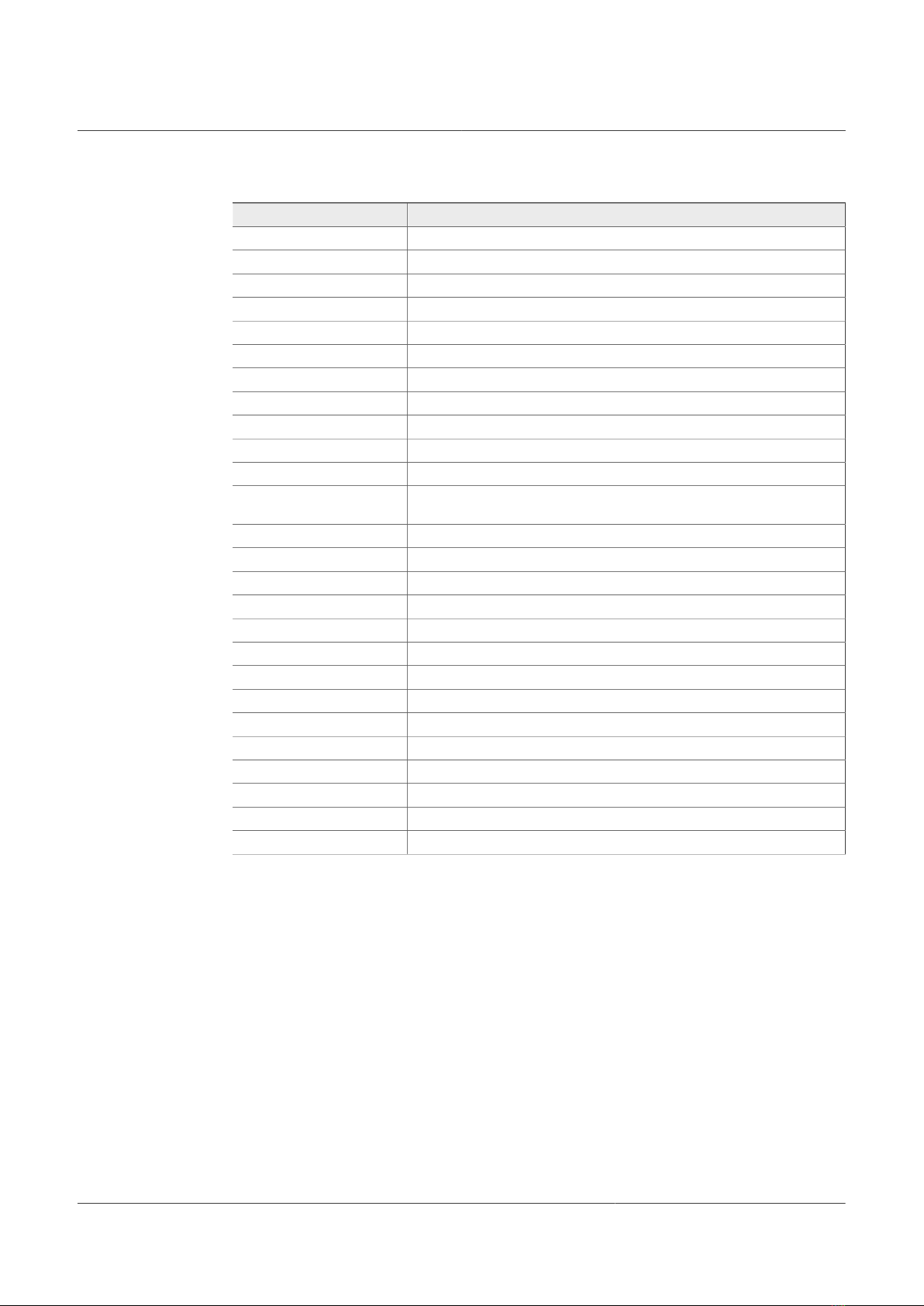

The RDGD31603PHSEVM is a fully functional three-phase inverter evaluation board

populated with six GD3160 gate drivers with fault management and supporting

circuitry. This board supports SPI daisy chain communication for programming and

communication with three high-side gate drivers and three low-side gate drivers

independently.

This board has low-voltage and high-voltage isolation in conjunction with gate drive

integrated galvanic signal isolation. Other supporting features on the board include

desaturation short-circuit detection, IGBT/SiC temperature sensing, DC Link bus voltage

monitoring, phase current sensing, and motor resolver excitation and signal processing

connection circuitry. See GD3160 data sheet for additional gate drive features.

2 Finding kit resources and information on the NXP web site

NXP Semiconductors provides online resources for this reference design and its

supported device(s) on http://www.nxp.com.

The information page for RDGD31603PHSEVM reference design is at http://

www.nxp.com/RDGD31603PHSEVM. The information page provides overview

information, documentation, software and tools, parametrics, ordering information

and a Getting Started tab. The Getting Started tab provides quick-reference

information applicable to using the RDGD31603PHSEVM reference design, including the

downloadable assets referenced in this document.

2.1 Collaborate in the NXP community

The NXP community is for sharing ideas and tips, ask and answer technical questions,

and receive input on just about any embedded design topic.

The NXP community is at http://community.nxp.com.

3 Getting ready

Working with the RDGD31603PHSEVM requires kit contents and a Windows PC

workstation with FlexGUI software installed.

3.1 Kit contents

•Assembled and tested RDGD31603PHSEVM (three-phase inverter populated with

5.0 V compatible gate driver devices) board in an anti-static bag

•3.3 V to 5.0 V translator board connected to FRDM-KL25Z MCU (KITGD3160TREVB)

with micro-USB cable for using FlexGUI software control

•Quick Start Guide

UM11063 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2021. All rights reserved.

User manual Rev. 1 — 18 August 2021

4 / 40