3DQDVRQLF

2

Contents

1 CIRCUIT DESCRIPTION...........................................................................................................................3

1.1 SMALL SIGNAL PART .................................................................................................................................3

1.1.1 Tuner and IF output Tuner:.............................................................................................................3

1.1.2 Vision IF ..........................................................................................................................................3

1.1.3 Sound...............................................................................................................................................8

1.1.4 Horizontal and vertical synchronization .......................................................................................10

1.1.5 Luminance and chrominance signal processing............................................................................13

1.1.6 Color Decoder...............................................................................................................................15

1.1.7 AFC - Tuning - ATS .......................................................................................................................18

1.2 DIGITAL CONTROL SIGNALS....................................................................................................................20

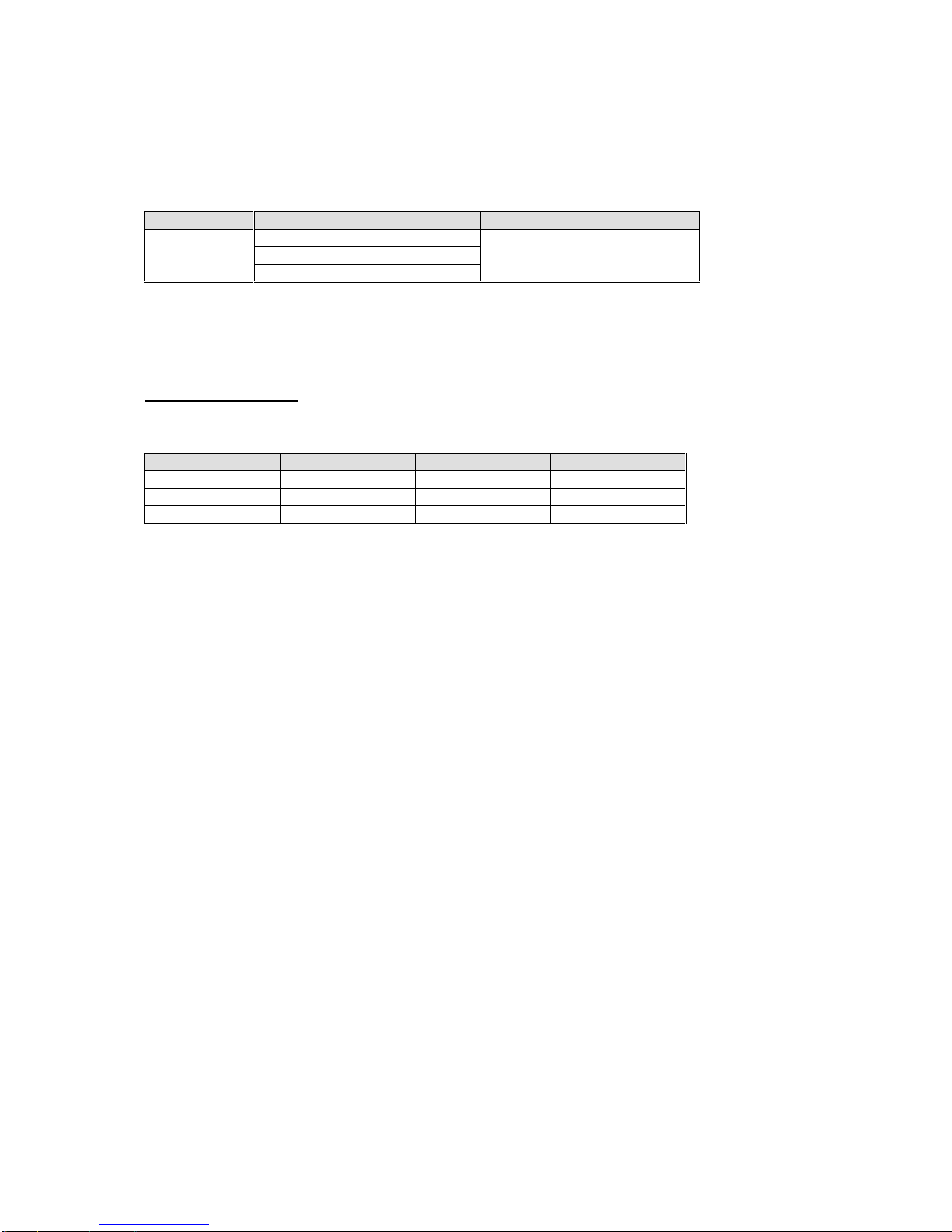

1.2.1 1-3-1 local keyboard......................................................................................................................20

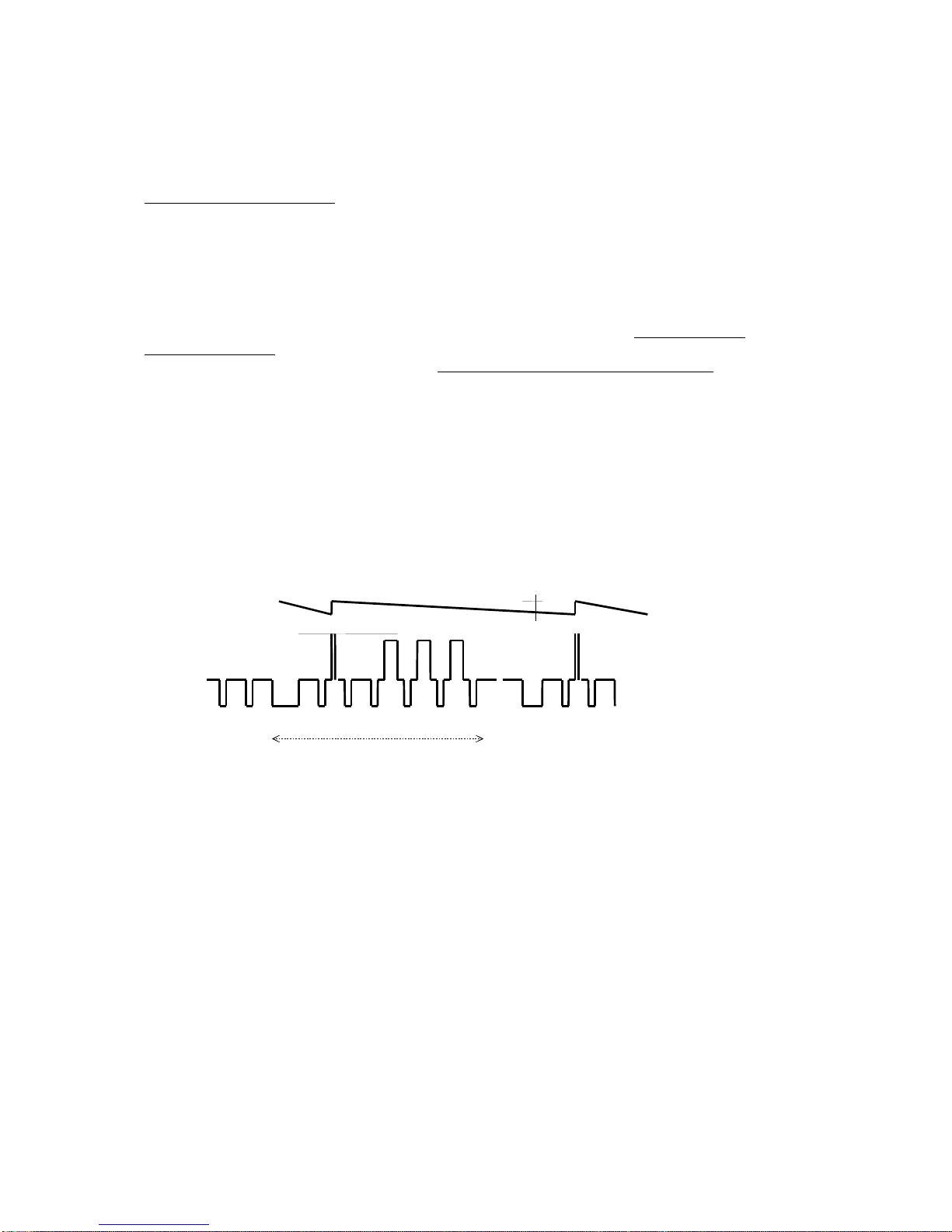

1.2.2 1-3-2 IR remote control code.........................................................................................................20

1.2.3 I2C bus...........................................................................................................................................22

1.3 HORIZONTAL DEFLECTION - FBT ...........................................................................................................24

1.3.1 General description:......................................................................................................................24

1.3.2 Horizontal deflection.....................................................................................................................24

1.4 VERTICAL DEFLECTION...........................................................................................................................29

1.4.1 Z-421 circuit ..................................................................................................................................29

1.4.2 Drive circuit part...........................................................................................................................30

1.5 VIDEO AMPLIFIER AND ABS...................................................................................................................32

1.5.1 Video output amplification.............................................................................................................32

1.5.2 ABS operation................................................................................................................................34

1.5.3 Beam current limiter......................................................................................................................35

1.5.4 Euro-scart......................................................................................................................................36

1.6 POWER SUPPLY STR-S5707....................................................................................................................37

1.6.1 Vin terminal, start-up circuit..........................................................................................................37

1.6.2 Oscillator, F/B terminal voltage (pin 7).........................................................................................37

1.6.3 Function of INH terminal (pin 6), control of off-time....................................................................37

1.6.4 Drive circuit...................................................................................................................................37

1.6.5 OCP function.................................................................................................................................37

1.6.6 Latch Circuit..................................................................................................................................38

1.6.7 Thermal shutdown circuit..............................................................................................................38

1.6.8 Over-voltage protection circuit......................................................................................................38

1.6.9 Stand-by Mode TOP210.................................................................................................................38

1.6.10 CONTROL PIN (pin4)...................................................................................................................38

2 VCR PART...................................................................................................................................................39

2.1 KEY FEATURES OF VIDEO IC AND ITS RELATIVES....................................................................39

2.2 RECORD AND PLAYBACK PROCESSING CIRCUIT .....................................................................40

2.2.1 RECORD PROCESSING...............................................................................................................40

2.2.2 PLAYBACK PROCESSING...........................................................................................................43

2.2.3 AUDIO SIGNAL PROCESSING (LA71511M) ..............................................................................46