PCI 6152 Data Book v2.0

2003 PLX Technology, Inc. All rights reserved. 8

9.2.2 ISA Mode................................................................................................................................... 60

9.3 MEMORY ADDRESS DECODING............................................................................................................ 60

9.3.1 Memory-Mapped I/O Base and Limit Address Registers .......................................................... 61

10 PCI BUS ARBITRATION ................................................................................................................. 62

10.1 PRIMARY PCI BUS ARBITRATION......................................................................................................... 62

10.2 SECONDARY PCI BUS ARBITRATION.................................................................................................... 62

11 TRANSACTION DELAY .................................................................................................................. 63

12 ERROR HANDLING ........................................................................................................................ 64

12.1 ADDRESS PARITY ERRORS.................................................................................................................. 64

12.2 DATA PARITY ERRORS........................................................................................................................ 65

12.2.1 Configuration Write Transactions to Configuration Space ........................................................ 65

12.2.2 Read Transactions .................................................................................................................... 65

12.3 DATA PARITY ERROR REPORTING SUMMARY ....................................................................................... 66

12.4 SYSTEM ERROR (SERR#) REPORTING ............................................................................................... 69

13 RESET.............................................................................................................................................. 70

13.1 PRIMARY INTERFACE RESET ............................................................................................................... 70

13.2 SECONDARY INTERFACE RESET .......................................................................................................... 70

14 BRIDGE BEHAVIOR ....................................................................................................................... 71

14.1 ABNORMAL TERMINATION (INITIATED BY BRIDGE MASTER)................................................................... 72

14.1.1 Master Abort.............................................................................................................................. 72

14.1.2 PCI Master on Primary Bus....................................................................................................... 72

14.2 CONFIGURATION TYPE #1 TO TYPE #0 CONVERSION ........................................................................... 72

14.3 CONFIGURATION TYPE #1 TO TYPE #1 BY-PASSING ............................................................................ 73

14.4 TYPE-0 CONFIGURATION CYCLE FILTER MODE .................................................................................... 73

14.5 DECODING ......................................................................................................................................... 73

14.6 SECONDARY MASTER ......................................................................................................................... 74

14.7 PCI CLOCK RUN FEATURE.................................................................................................................. 74

15 CLOCKS .......................................................................................................................................... 75

15.1 PRIMARY AND SECONDARY CLOCK INPUTS .......................................................................................... 75

15.2 SECONDARY CLOCK OUTPUTS ............................................................................................................ 75

16 66-MHZ OPERATION ...................................................................................................................... 76

17 MISCELLANEOUS OPTIONS ......................................................................................................... 77

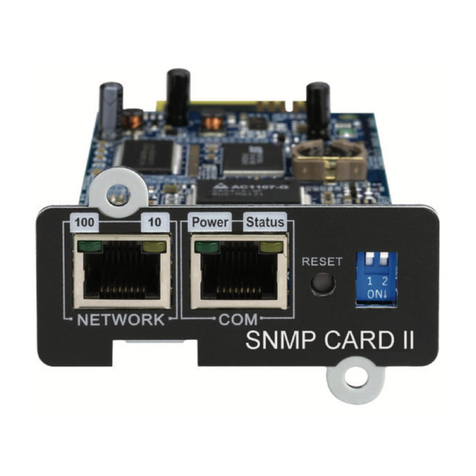

17.1 EEPROM INTERFACE ........................................................................................................................ 77

17.1.1 Auto Mode EEPROM Access.................................................................................................... 77

17.1.2 EEPROM Mode at Reset .......................................................................................................... 77

17.1.3 EEPROM Data Structure .......................................................................................................... 78

17.1.4 EEPROM Address and Corresponding PCI 6152 Register ...................................................... 79

17.2 GENERAL PURPOSE I/O INTERFACE .................................................................................................... 80

17.3 VITAL PRODUCT DATA ........................................................................................................................ 80

18 PCI POWER MANAGEMENT.......................................................................................................... 81

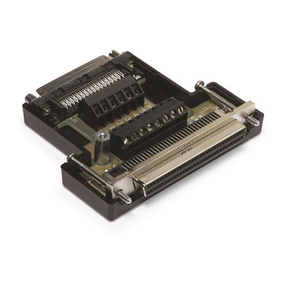

19 HOT SWAP ...................................................................................................................................... 82

19.1 HOT SWAP INSERTION ........................................................................................................................ 82

19.2 HOT SWAP EXTRACTION ..................................................................................................................... 82