ZL2005PEVK4 USER MANUAL

AN1464 Rev.1.2 Page 2 of 18

May 7, 2009

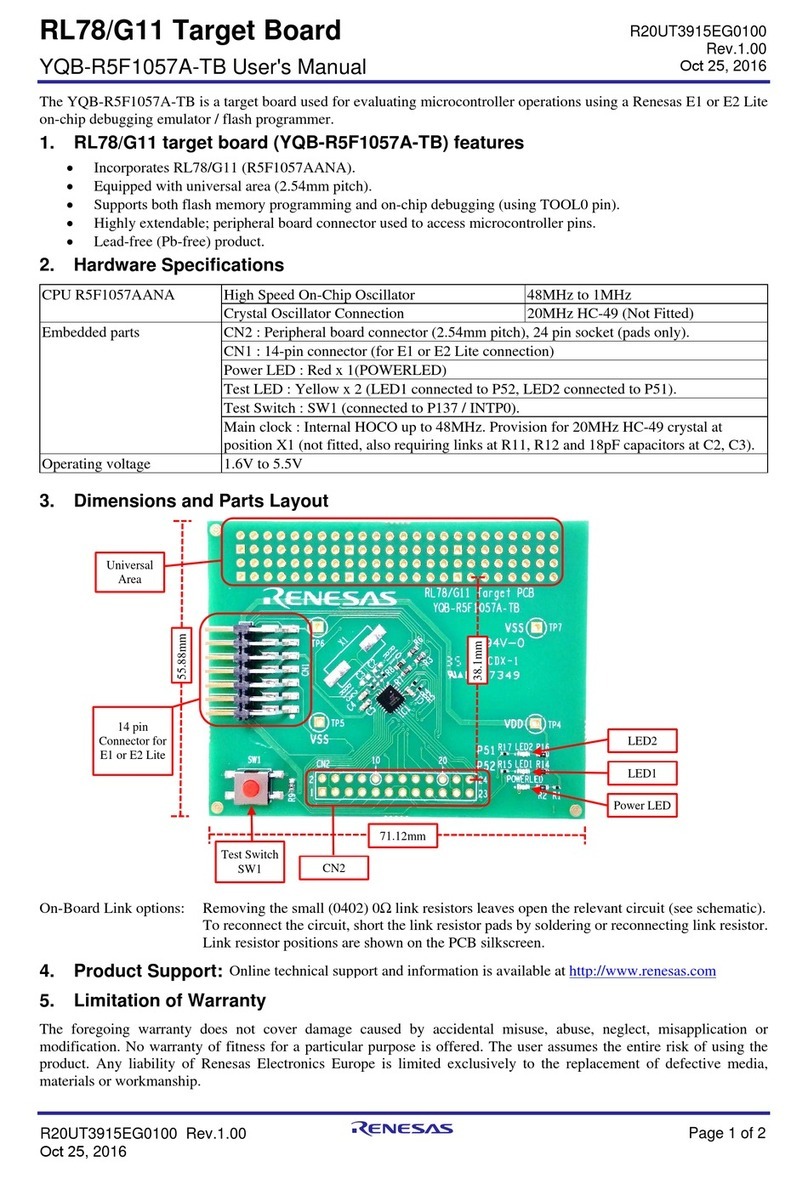

Functional Description

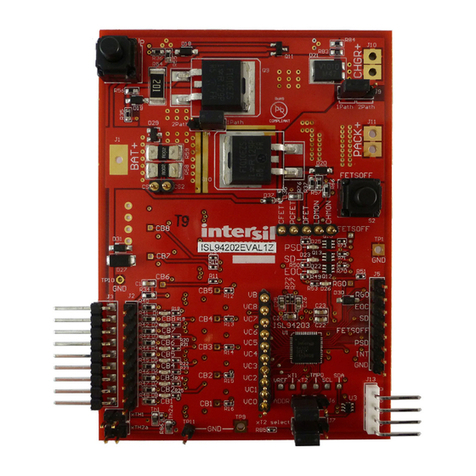

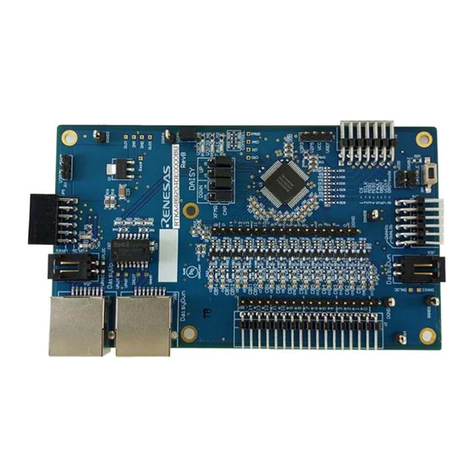

The FG ZL2005PEVK4 provides the circuit required to

demonstrate the features of the ZL2005P in a 10A

configuration. The FG ZL2005PEVK4 has a

functionally-optimized layout that allows highly-efficient

operation to its maximum output current (see Figure 2).

The input power connection is provided through banana

jack terminals. Stand-alone operation of the ZL2005P is

achieved by factory installed pin-strap settings and

pre-configuration via PMBus commands. PMBus protocol

communication is performed via a SMBus interface using

an external USB to SMBus adaptor. PMBus commands

can be used to modify the settings of the evaluation

platform.

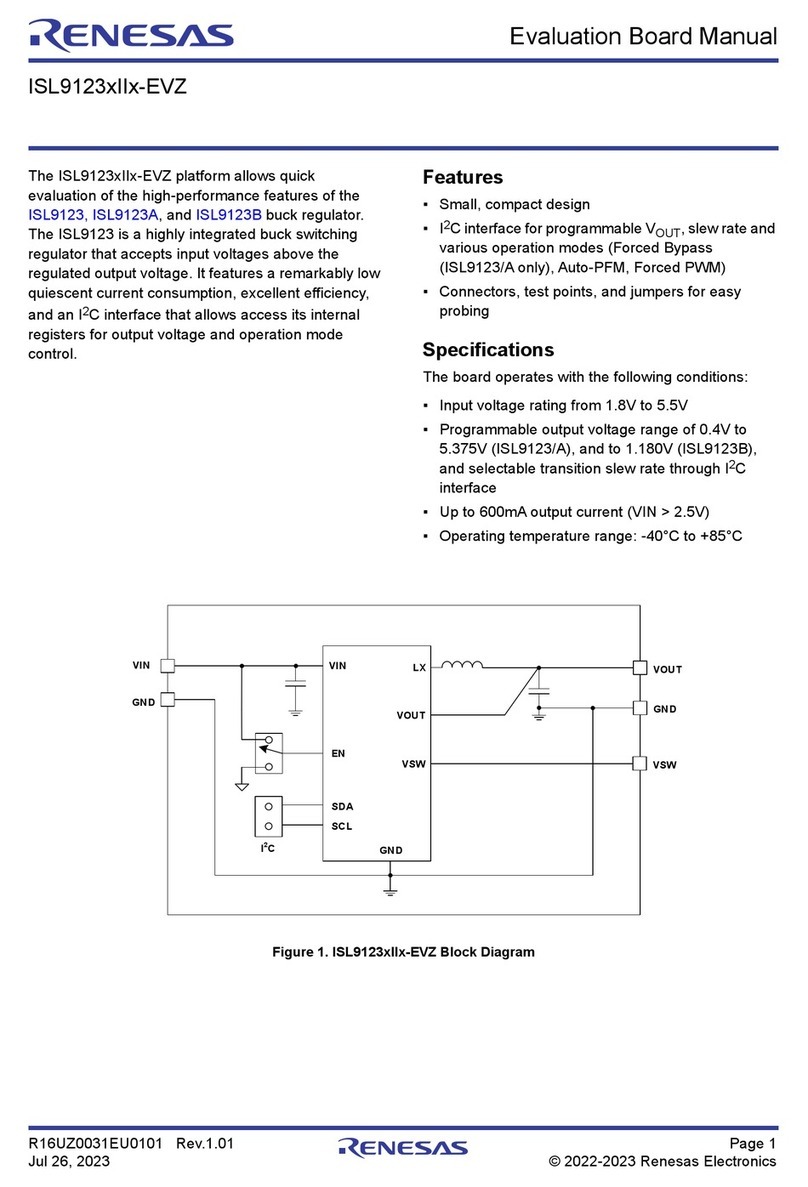

Figure 3 shows the ZL2005P circuit schematic. The circuit

consists of the ZL2005P power conversion and

management IC with its minimal component count.

The input voltage connection is made at J1 which is

labeled VIN±. J2 is the output connector for the output

voltage, VOUT±. The VIN± and VOUT± connections are

rated to 10A.

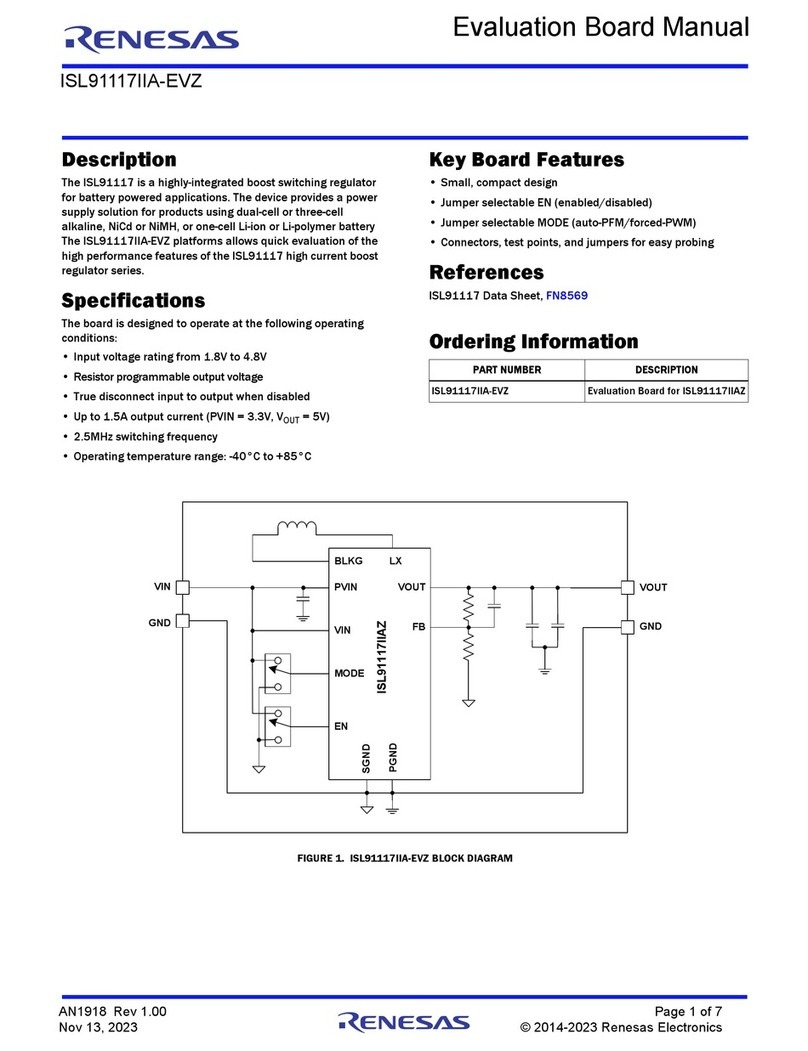

Figure 4 shows the FG ZL2005PEVK4 interface

schematic. It contains various circuits that interface to

the ZL2005P’s circuit. The hardware enable function is

controlled by a toggle switch (SW1) on the FG

ZL2005PEVK4 board. External temperature is monitored

from a 2N3904 transistor (Q3) connected to the XTEMP

pin. This external temperature is read with the

READ_TEMPERATURE_2 PMBusTM command. The power

good status is indicated by the PG LED at D11. The PG

LED indicates the correct state of the power good signal

when power is applied to the FG ZL2005PEVK4 board.

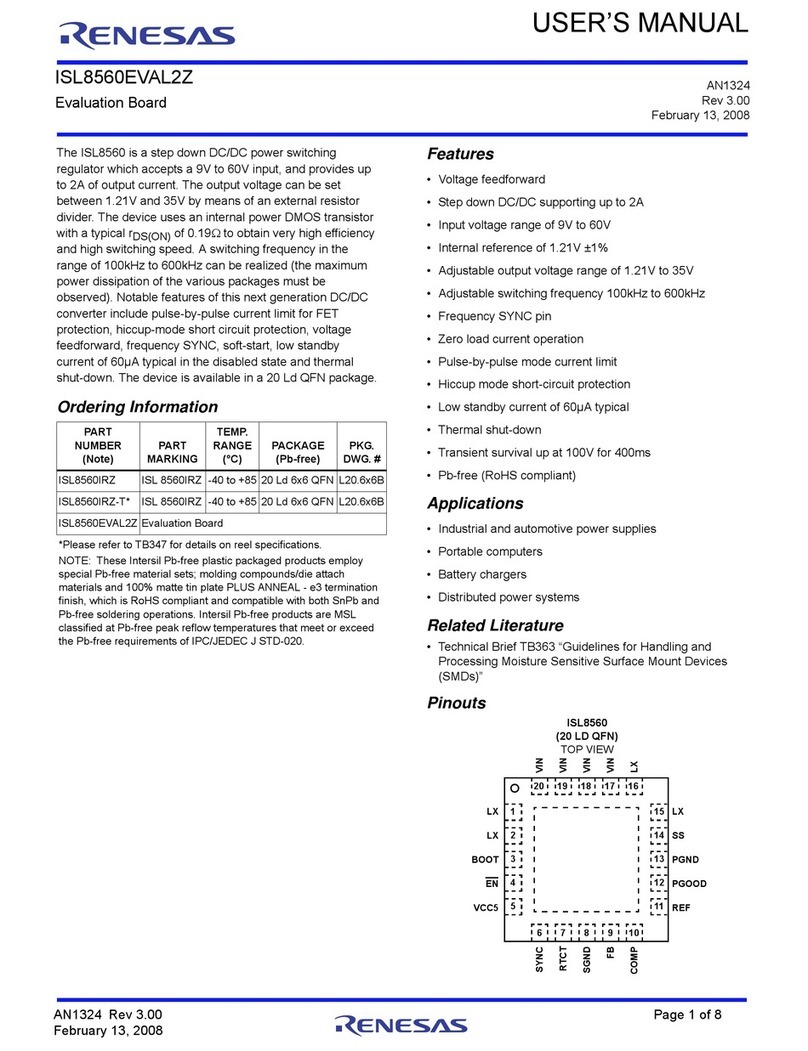

The right angle headers at opposite ends of the board

(J10 and J11) are available to daisy chain multiple

boards. The SMBus and Enable signals are passed

between these connectors. All header pins and switch

positions are labeled on the FG ZL2005PEVK4 board’s

silkscreen as shown in Figure 5.

The ZL2005P SMBusTM address is set by the jumper

applied to J12. The SA1 pin is strapped by an 11kΩ

resistor to ground. The J12 jumper applies a different

resistor to the SA0 pin to achieve the indicated SMBus

address settings. Note that power must be cycled to set a

new address.

Refer to Figures 5 through 10 for component placement

and board layout. The board layout has been optimized

for two-sided component area and thermal performance.

For ZL2005P circuit layout design considerations refer to

Zilker Labs Application Note AN10 (Reference 1 on

page 18).

Operation

Stand-Alone Operation

The FG ZL2005PEVK4 is easy to setup and operate. It is

configured, out of the box, to provide 1.2V at 10A from a

12V source. All input and output connections should be

made before turning the input supply on.

When the input power supply is turned on, and the

enable switch is set to enable, the ZL2005P will output

the configured voltage. A load can be applied to the

output and the circuit can be tested.

PMBus Operation

The ZL2005P utilizes the PMBus protocol. The PMBus

functionality can be accessed via USB from a PC running

the Zilker Labs Evaluation software on a Windows XP or

Windows 2000/NT operating system.

Install the Zilker Labs Evaluation software using the CD

included in the FG ZL2005PEVK4 kit or download it from

the web at www.zilkerlabs.com.

For PMBus operation, connect a USB to SMBus adaptor

(J2) to the EVB (J10). Apply a USB cable between the

USB to SMBus adaptor and the PC. Connect the output of

the FG ZL2005PEVK4 to the desired load. Then connect

an appropriate power supply to the input. Place the

enable switch in “DISABLE” and turn on the power.

Invoke the ZL2005P interface software.

The Zilker Labs Evaluation software allows modification

of all ZL2005P PMBus parameters. Manually configure

the ZL2005P with the interface software or load a

predefined configuration from a configuration text file.

Use the mouse-over pop-ups for help with the Zilker Labs

Evaluation software. Refer to the Zilker Labs Application

Note AN13 (Reference 3 on page 18) for PMBus details.

The enable switch can then be moved to “ENABLE” and

the ZL2005P can be tested. Alternatively, the PMBus

commands ON_OFF_CONFIG and OPERATION may be

used to manipulate the enable state.

Modifying the FG ZL2005PEVK4

In order to design and test an alternative power train

circuit with the ZL2005P, choose a desired operating

conditions and power train. Enter the selected power

design parameters into Zilker Labs’ PID

calculation/simulation tool. The results from the

simulation tool provide appropriate compensation values

to configure the new ZL2005P circuit. Apply the new

power train circuit to the evaluation board. Power the

board and invoke the evaluation software. Then

configure the new PID coefficients using the “PMBus:

Basic” command page or loading a configuration text file

with the new compensation coefficients in it.