RT7247A

10 DS7247A-03 October 2016www.richtek.com

©

Copyright 2016 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

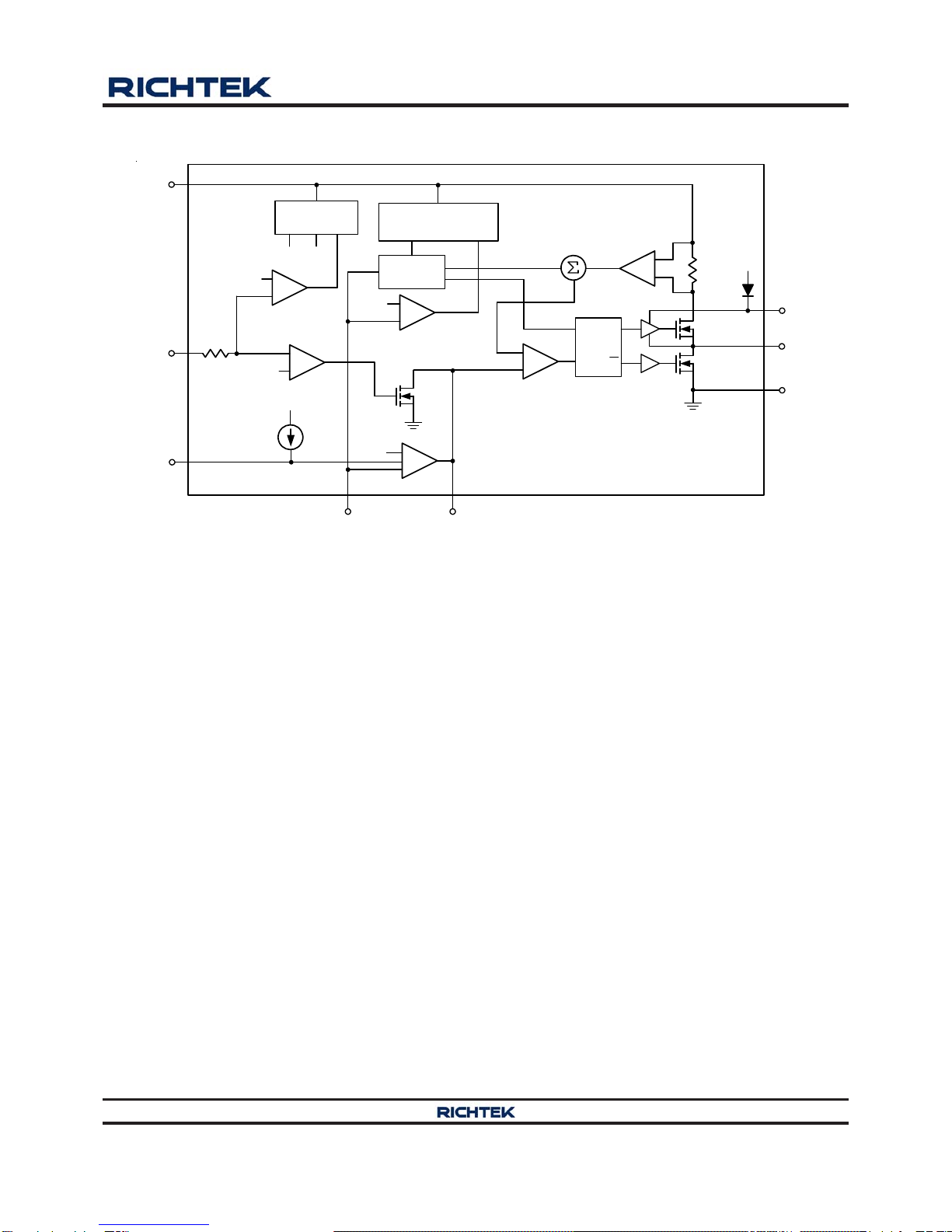

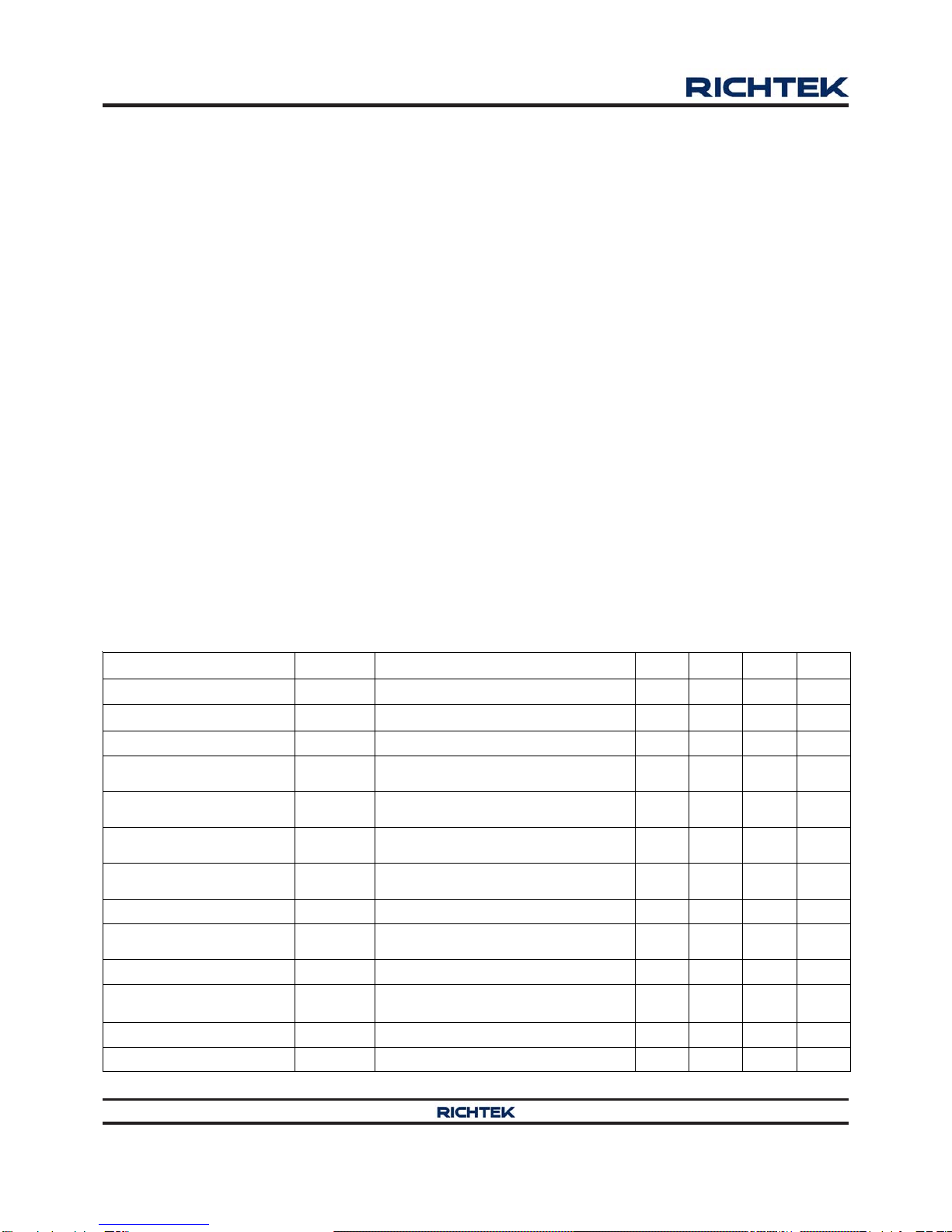

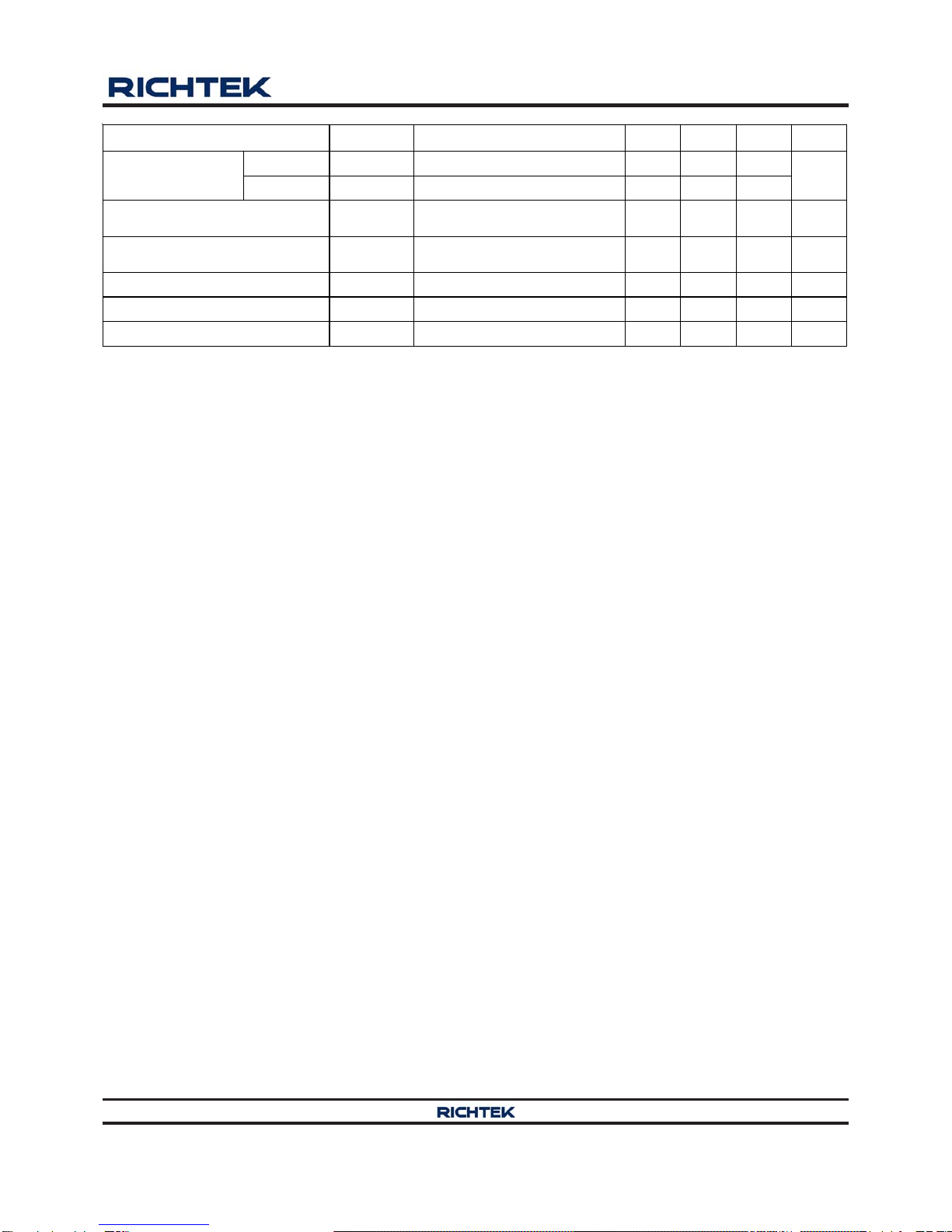

Application Information

Output Voltage Setting

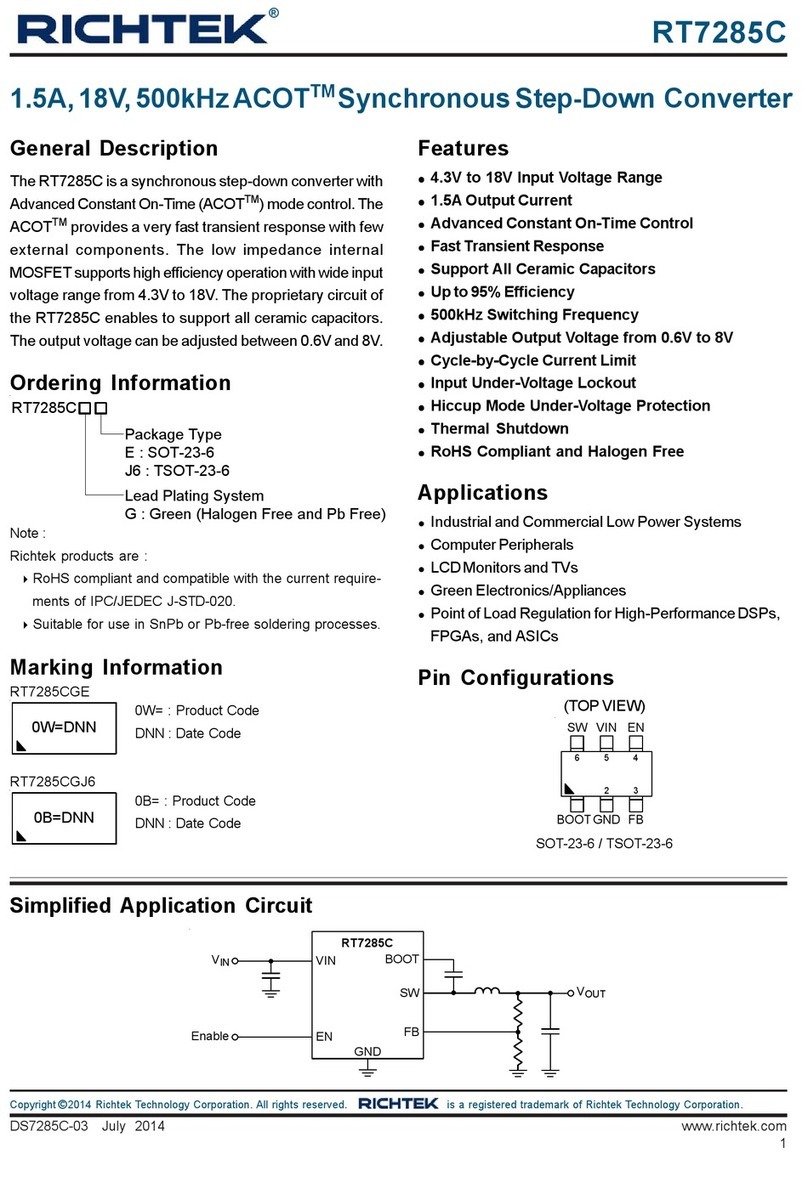

TheresistivedividerallowstheFBpin to sense the output

voltage as shown in Figure 1.

Figure 1. Output Voltage Setting

The output voltage is set by an external resistive voltage

divideraccordingto the followingequation:

OUT REF R1

V =V 1

R2

Where VREF is the reference voltage (0.8V typ.).

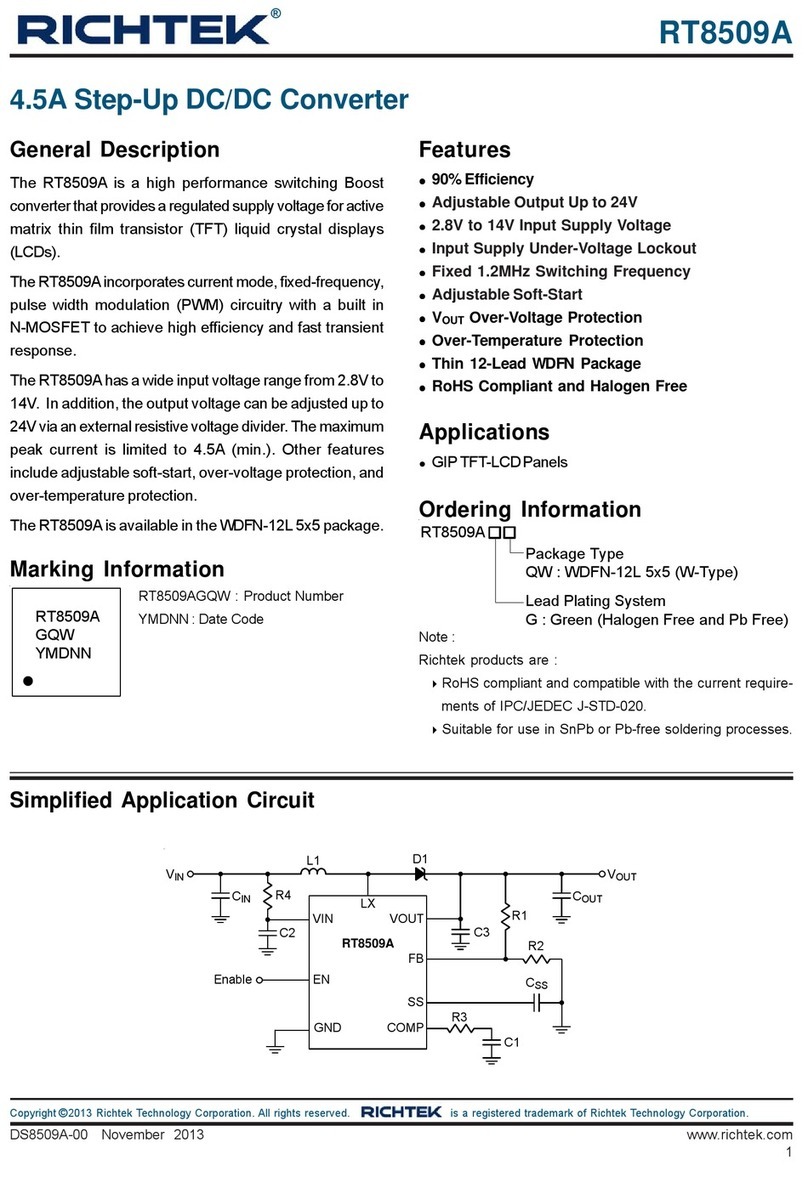

External Bootstrap Diode

Connecta0.1μFlowESRceramic capacitor between the

BOOT pin and SW pin. This capacitor provides the gate

drivervoltageforthehighsideMOSFET.

It is recommended to add an external bootstrap diode

between an external 5V and BOOT pin for efficiency

improvementwheninputvoltageis lowerthan5.5Vorduty

ratio is higher than 65% .The bootstrap diode can be a

low cost one such as IN4148 or BAT54. The external 5V

can be a 5V fixed input from system or a 5V output of the

RT7247A. Note that the external boot voltage must be

lowerthan 5.5V

Figure 2. External BootstrapDiode

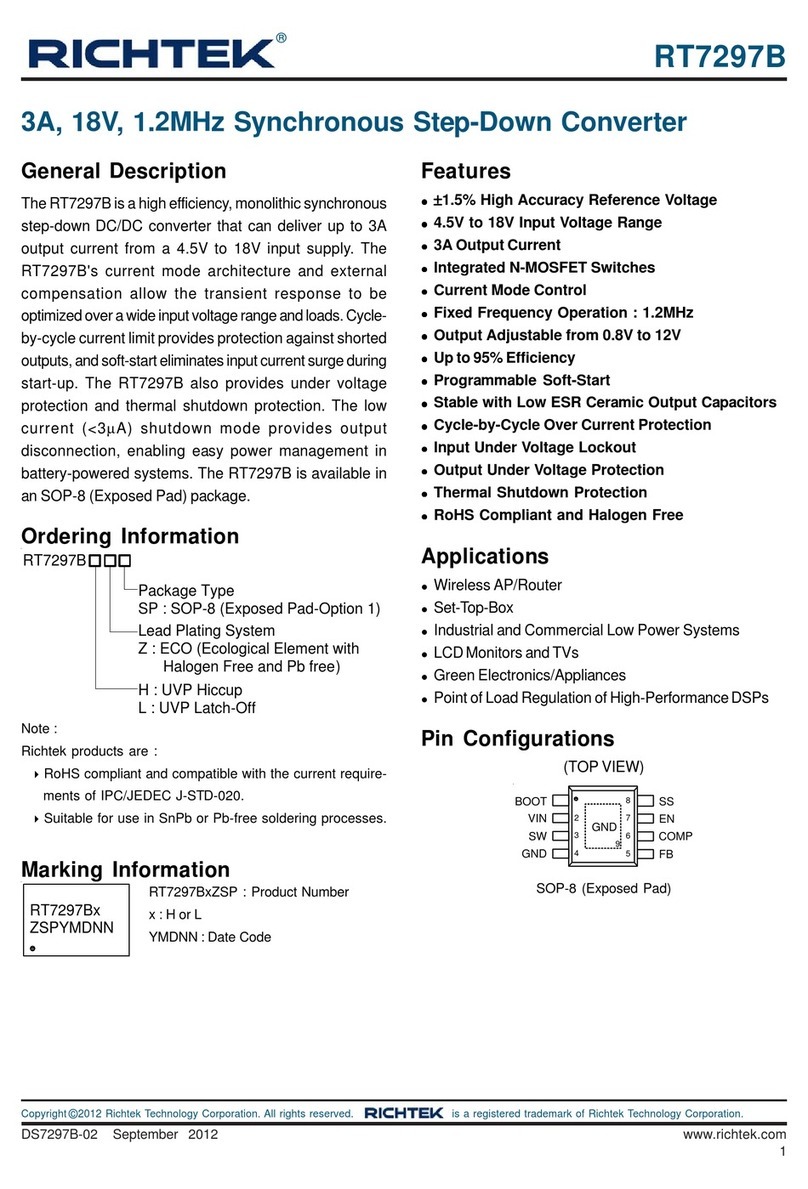

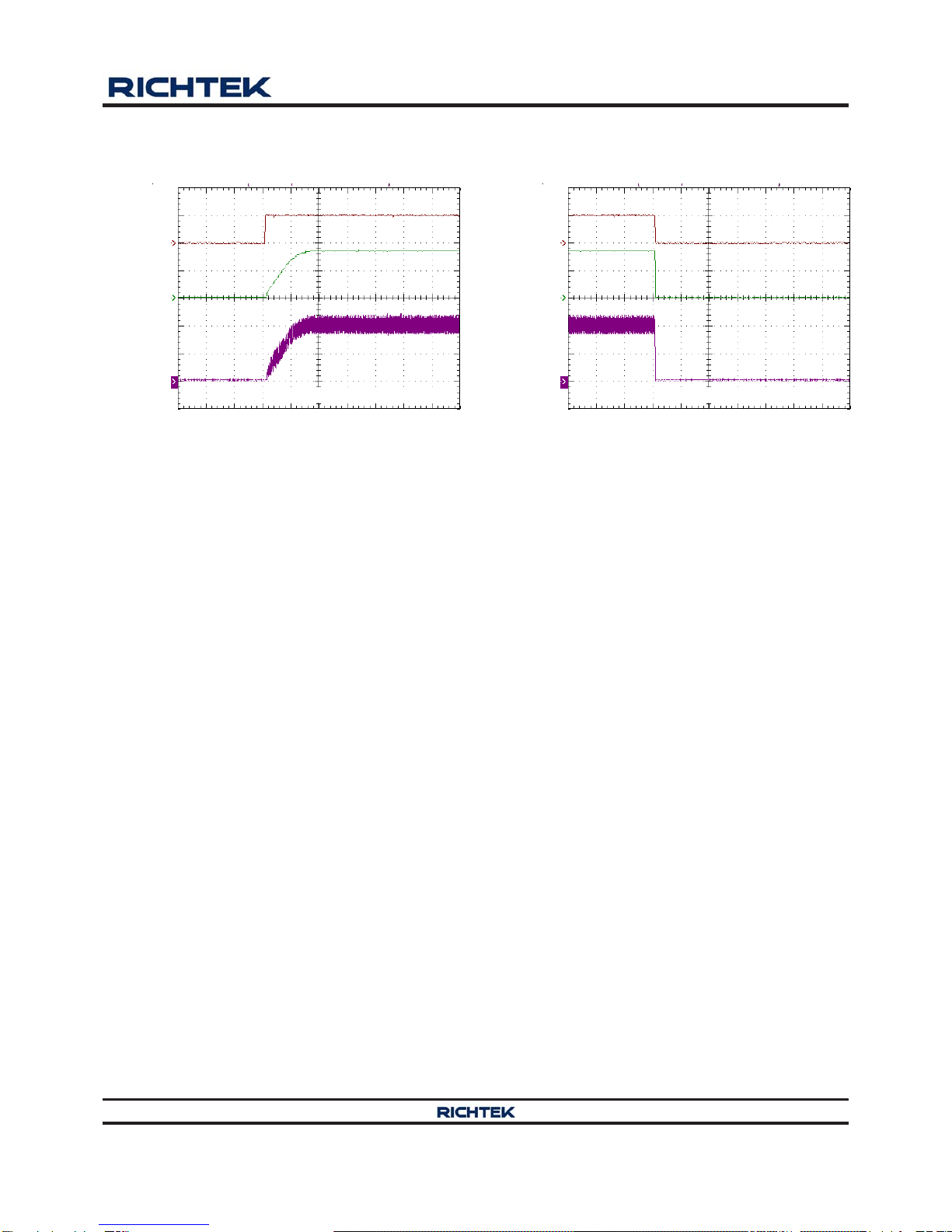

Chip Enable Operation

The EN pin is the chip enable input. Pulling the EN pin

low (<0.4V) will shut down the device. During shutdown

mode,theRT7247A quiescentcurrentdropstolower than

3μA.Driving the ENpin high (>2V, <18V) will turn on the

device again. For external timing control, the ENpin can

also be externally pulled high by adding a REN resistor

and CEN capacitor from theVINpin (see Figure 3).

Soft-Start

The RT7247A provides soft-start function. The soft-start

function is used to prevent large inrush current while

converter is being powered-up. The soft-start timing can

beprogrammedbytheexternalcapacitorbetweenSSand

GND. An internal current source ISS (6μA) charges an

external capacitor to build a soft-start ramp voltage. The

VFB voltagewilltracktheinternalramp voltage duringsoft-

start interval. The typical soft start time is calculated as

follows :

SS

SS SS

SS

0.8 C

Soft-Start time t = , if C capacitor

I0.8 0.1

is 0.1 F, then soft-start time = 13.5ms

6

≒

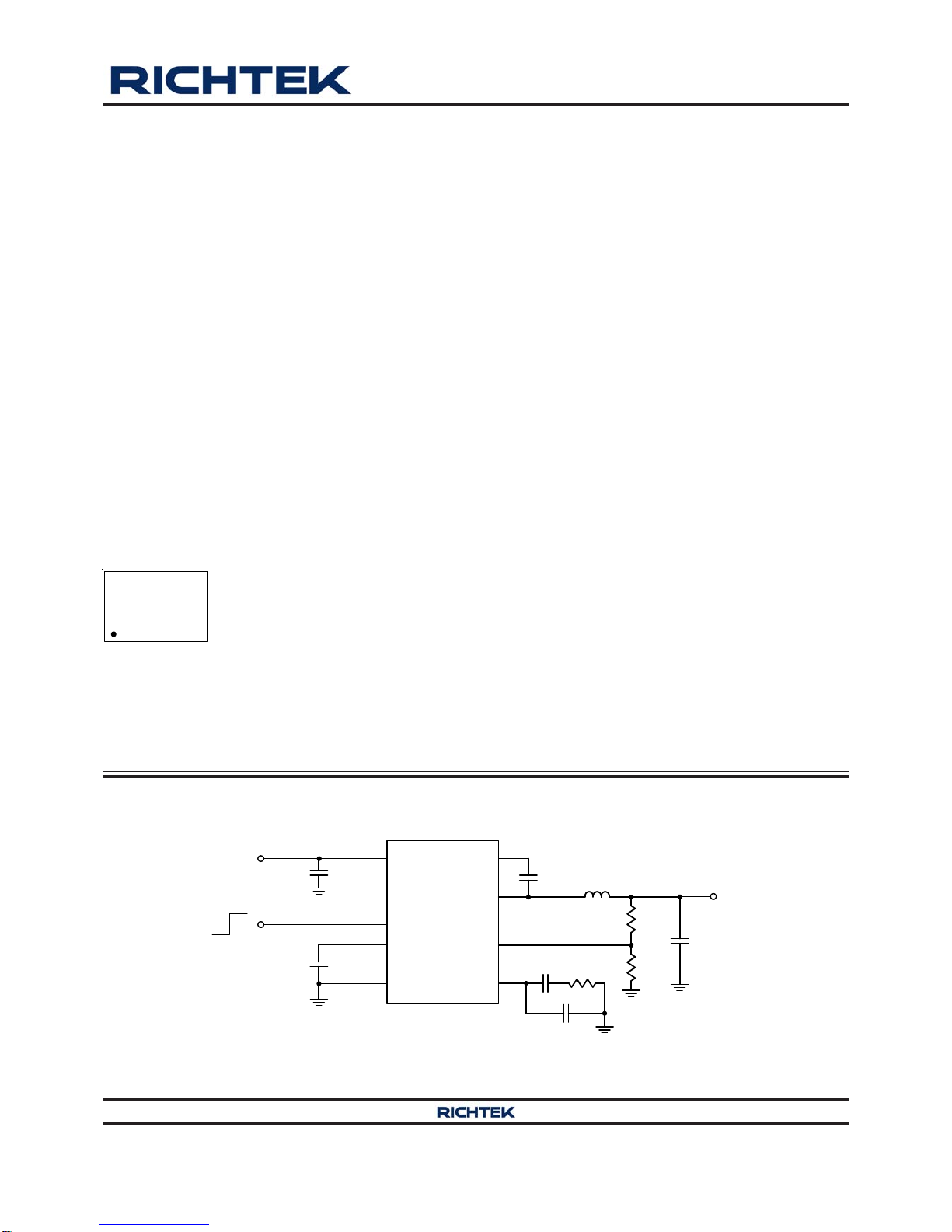

An external MOSFET can be added to implement digital

controlontheENpin when nosystemvoltageabove2.5V

is available, as shown in Figure 4. In this case, a 100kΩ

pull-up resistor, REN, is connected between VIN and the

EN pin. MOSFET Q1 will be under logic control to pull

down the EN pin.

Figure3.EnableTimingControl

Figure 4.Digital Enable Control Circuit

RT7247A

GND

FB

R1

R2

VOUT

SW

BOOT

5V

RT7247A 100nF

RT7247A

EN

GND

VIN REN

CEN

EN

RT7247A

EN

GND

100k

VIN

REN

Q1

EN