RTD Embedded Technologies, Inc. | www.rtd.com vi FPGA35S6046/FPGA35S6101 User’s Manual

Table of Figures

Figure 1: Board Dimensions ................................................................................................................................................................................... 11

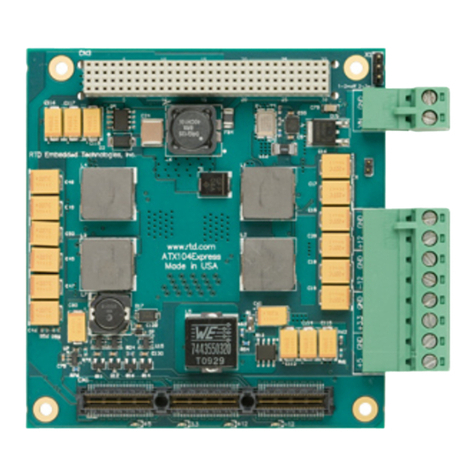

Figure 2: Board Connections .................................................................................................................................................................................. 12

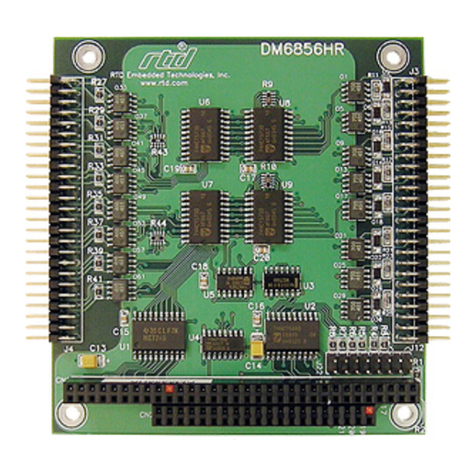

Figure 3: Example 104™Stack............................................................................................................................................................................... 16

Figure 4: IDAN Dimensions .................................................................................................................................................................................... 17

Figure 5: Example IDAN System ............................................................................................................................................................................ 23

Figure 6: FPGA35S6 Block Diagram...................................................................................................................................................................... 24

Figure 7: CN9 Digital I/O Circuitry .......................................................................................................................................................................... 25

Figure 8: Serial Port Transceiver............................................................................................................................................................................ 25

Table of Tables

Table 1: Ordering Options ........................................................................................................................................................................................ 9

Table 2: Operating Conditions ................................................................................................................................................................................ 10

Table 3: Electrical Characteristics .......................................................................................................................................................................... 10

Table 4: CN3 Programming Header ....................................................................................................................................................................... 12

Table 5: CN8 I/O Pin Assignments ......................................................................................................................................................................... 13

Table 6: CN9 I/O Pin Assignments ......................................................................................................................................................................... 14

Table 7: CN10, CN11, CN12, CN13 I/O Pin Assignments ..................................................................................................................................... 14

Table 8: Pull up/Pull down Jumper options ............................................................................................................................................................ 15

Table 9: JP1 –Embedded Programmer Enable..................................................................................................................................................... 15

Table 10: JP8 –User ID Jumper ............................................................................................................................................................................ 15

Table 11: B2 Pull up Voltage .................................................................................................................................................................................. 15

Table 12: P2 Pin Assignments................................................................................................................................................................................ 18

Table 13: P3 Pin Assignments................................................................................................................................................................................ 19

Table 14: P4 Pin Assignments................................................................................................................................................................................ 20

Table 15: Pull up/Pull down Jumper options .......................................................................................................................................................... 22

Table 16: JP1 –Embedded Programmer Enable................................................................................................................................................... 22

Table 17: JP8 –User ID Jumper ............................................................................................................................................................................ 22

Table 18: B2 Pull up Voltage .................................................................................................................................................................................. 22

Table 19: Transceiver Configuration....................................................................................................................................................................... 26

Table 20: Identifying the FPGA35S6 ...................................................................................................................................................................... 27

Table 21: FPGA Example Register Map................................................................................................................................................................. 27