i

Table of Contents

1.

2.

3.

4.

5.

6.

7.

8.

1.

2.

3.

4.

5.

1.

2.

3.

4.

5.

6.

7.

8.

Part 1Chassis Description

Chassis Summary ........................................................................3

CPU. ......................................................................................&-18

2.1 A.DKeyldentification ...............................................................................................6

2.2 Option Switches ...................................................................................................7.9

2.3 Power On/ Standby ................................................................................................lO

2.4 Power Protection ...................................................................................................ll

2.5 Band Switching .....................................................................................................l2

2.6 Am ...............................................................................................................l3.l4

2-7 TV/AV switch Output ..............................................................................................l5

2.8 Analogue Controls Output ....................................................................................l5.l6

2-9 System Switch Output ........................................................................................l7.l8

2-10 H/Vpulse input ...................................................................................................l9

IF/Video/Chroma/Deflection ......................................................20-21

3-1 lFstage .............................................................................................................2O

3-2 Mdeo/Chroma stage .............................................................................................2l

3-3 Deflection Stage ..................................................................................................2l

System Switches ....................................................................22-23

4-1 Sound Carrier Trap ...............................................................................................22

4.2 SIFFiltering ........................................................................................................23

Audio Output .............................................................................24

Vertical Output ...........................................................................25

Horizontal Output .......................................................................26

Power Consumption Saving Circuit ................................................27

Part 2Block Diagram of K%

LA7687 cl F/Video/Chroma/Deflection> .............................................28

LC89950 <1 HDelay line> ..............................................................29

LA7642 <SECAM Decoder> ...........................................................29

LA7837 cVertical Output> .............................................................30

LA4285, LA4287 cAudio Output> ....................................................30

Part 3Trouble Shooting Chart

Common start point ....................................................................32

Dead ....................................................................................33-35

No picture/No sound ................................................................36-37

Uo picture-sound OK ...................................................................38

No sound-picture OK ...................................................................39

No colour ..................................................................................Ao

ncorrect colour phase .................................................................Al

Uo vertical deflection ...................................................................A2

Uo on-screen display ...................................................................A3

-2-

.

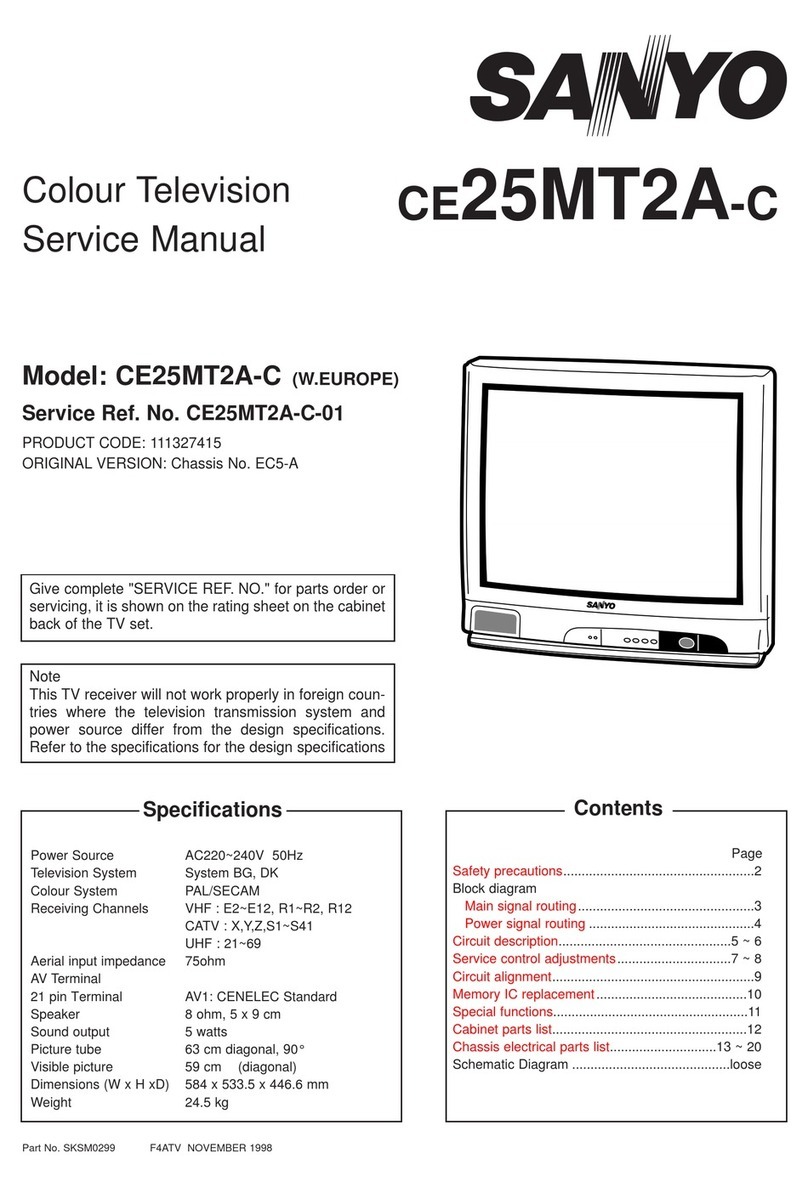

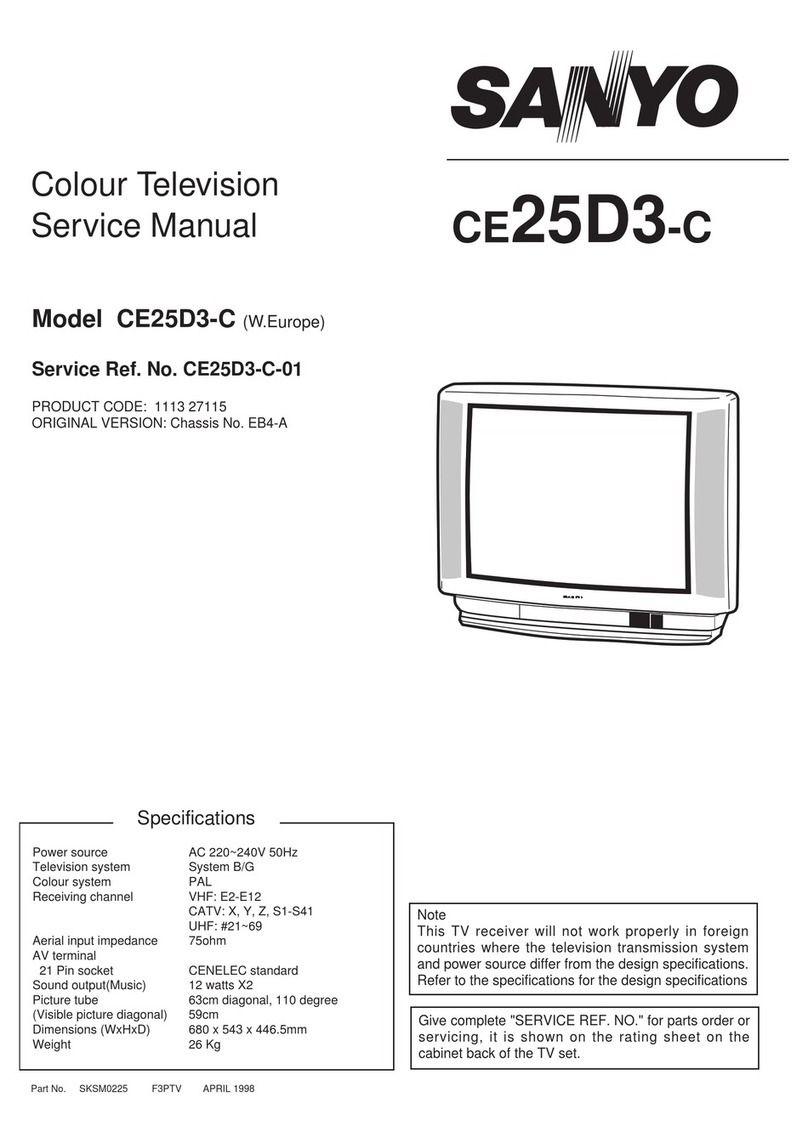

Training Manual AC 1Chassis