Contents

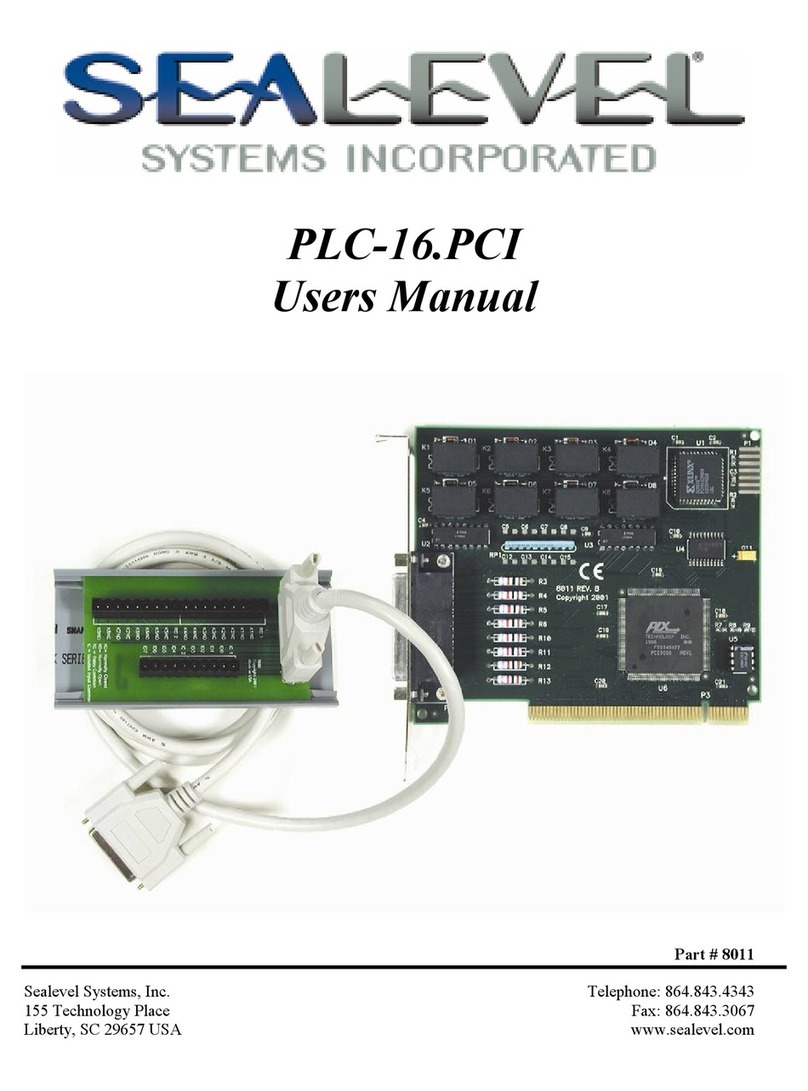

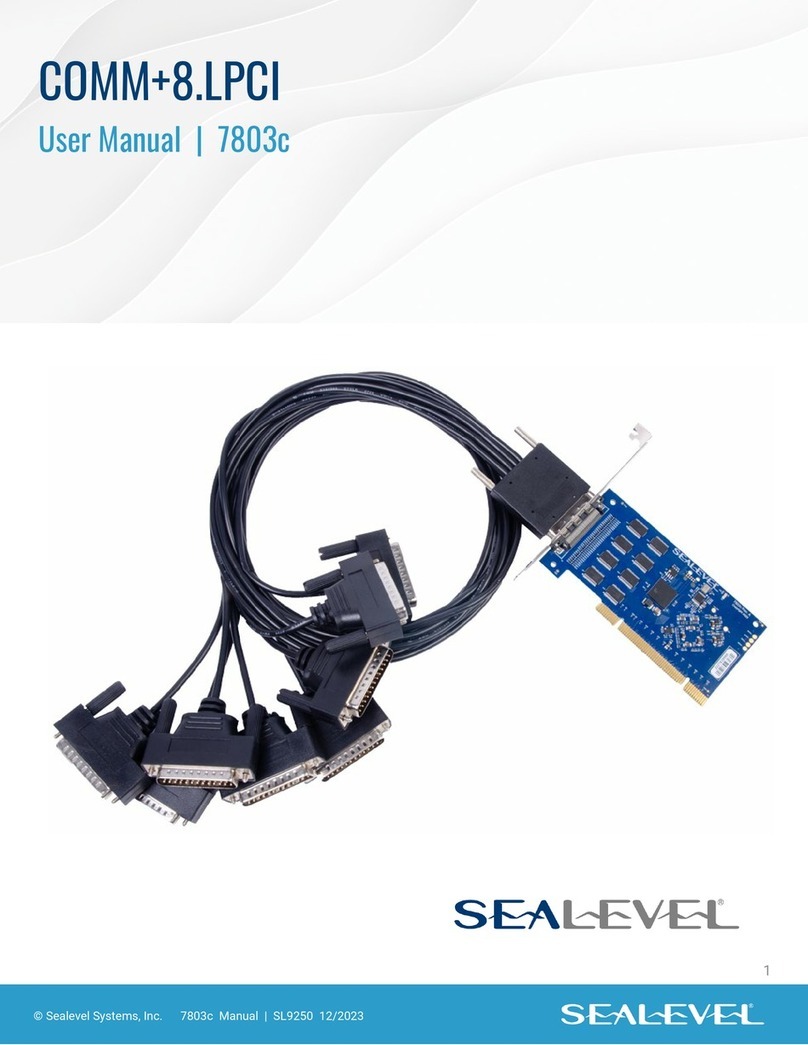

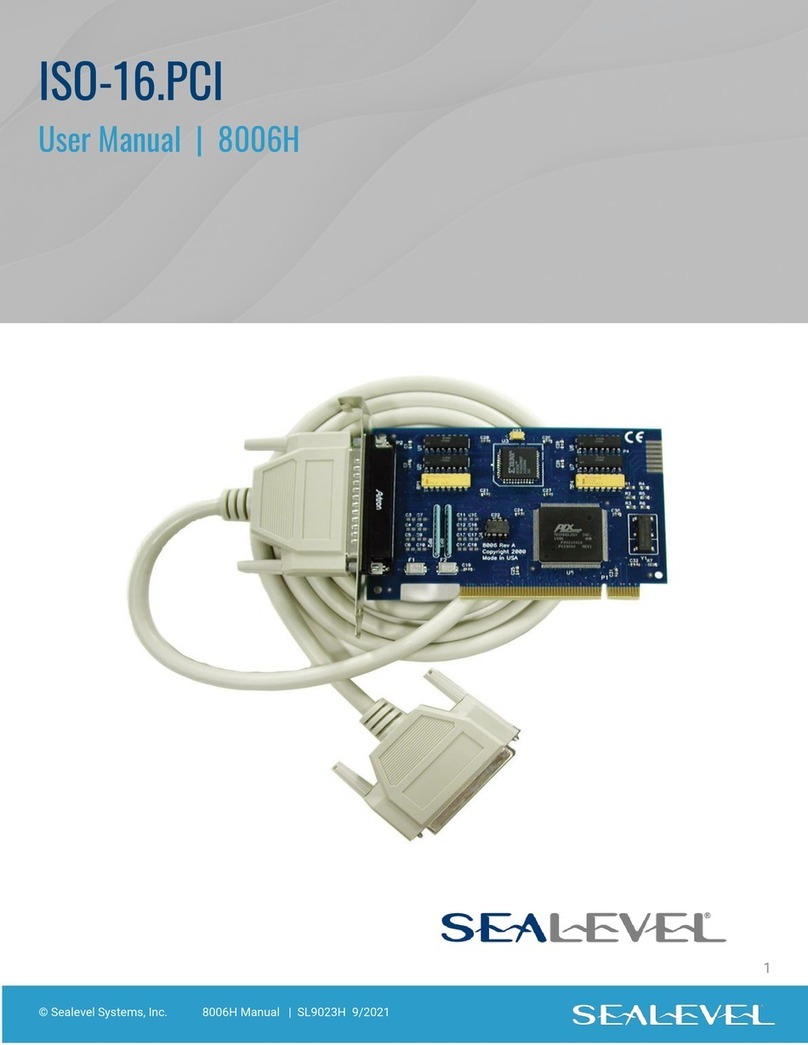

INTRODUCTION..................................................................................................1

OVERVIEW .................................................................................................................1

WHAT’S INCLUDED....................................................................................................1

INSTALLATION.................................................................................................1

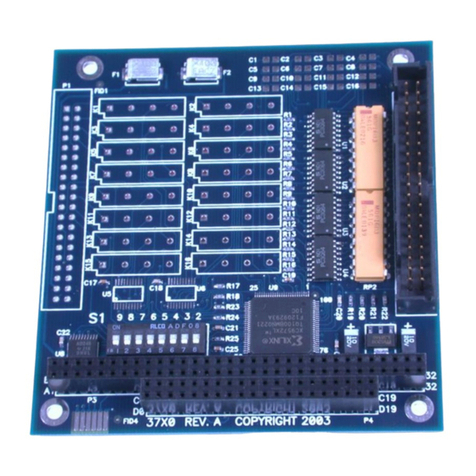

CARD SETUP..............................................................................................................1

SOFTWARE INSTALLATION ........................................................................................1

Linux Users.....................................................................................................1

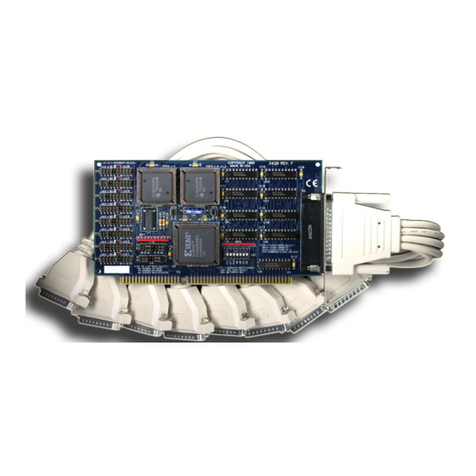

SYSTEM INSTALLATION .............................................................................................2

TECHNICAL DESCRIPTION............................................................................3

SOFTWARE ................................................................................................................3

LINUX USERS.............................................................................................................3

3RD PARTY SOFTWARE SUPPORT................................................................................4

ELECTRICAL CHARACTERISTICS.................................................................................5

Pull Ups...........................................................................................................6

50 pin ribbon cable pin out..........................................................................7

PROGRAMMING................................................................................................8

APPLICATION PROGRAMMERS INTERFACE (API) .......................................................8

Reading the Inputs:.......................................................................................8

Reading the Outputs:....................................................................................8

Presetting an Output Port:...........................................................................8

Writing the Outputs:.....................................................................................8

Interrupts:.......................................................................................................8

Port Configuration:......................................................................................9

Relative Addressing vs. Absolute Addressing........................................10

Addressing Continued...............................................................................12

DIRECT HARDWARE CONTROL...............................................................................14

Reading the Inputs:....................................................................................14

Reading the Outputs:.................................................................................14

Presetting an Output Port:........................................................................14

Writing the Outputs:..................................................................................14

Port Configuration:...................................................................................14

Interrupts.....................................................................................................14

Register Description (for direct hardware control)..............................15

Control Words.............................................................................................16

SPECIFICATIONS............................................................................................18

ENVIRONMENTAL SPECIFICATIONS..........................................................................18

POWER CONSUMPTION...........................................................................................18