ST X-NUCLEO-GFX01M Series User manual

Other ST Computer Hardware manuals

ST

ST STLINK-V3PWR User manual

ST

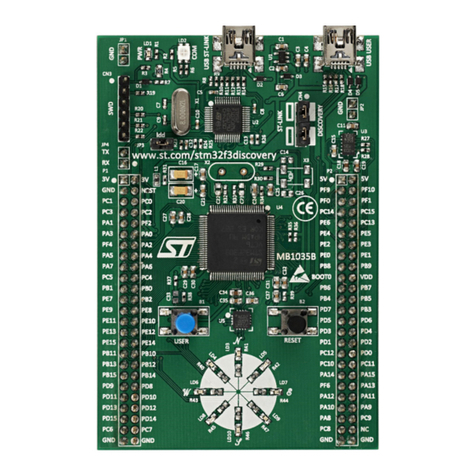

ST STM32F3DISCOVERY User manual

ST

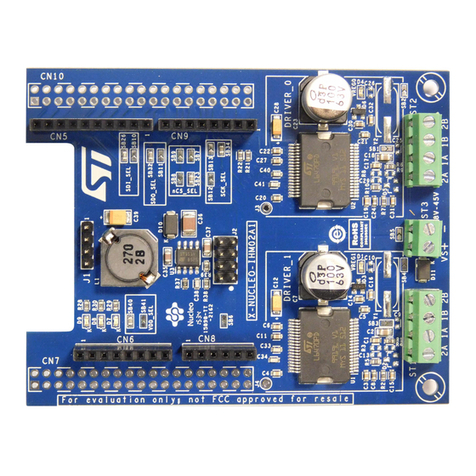

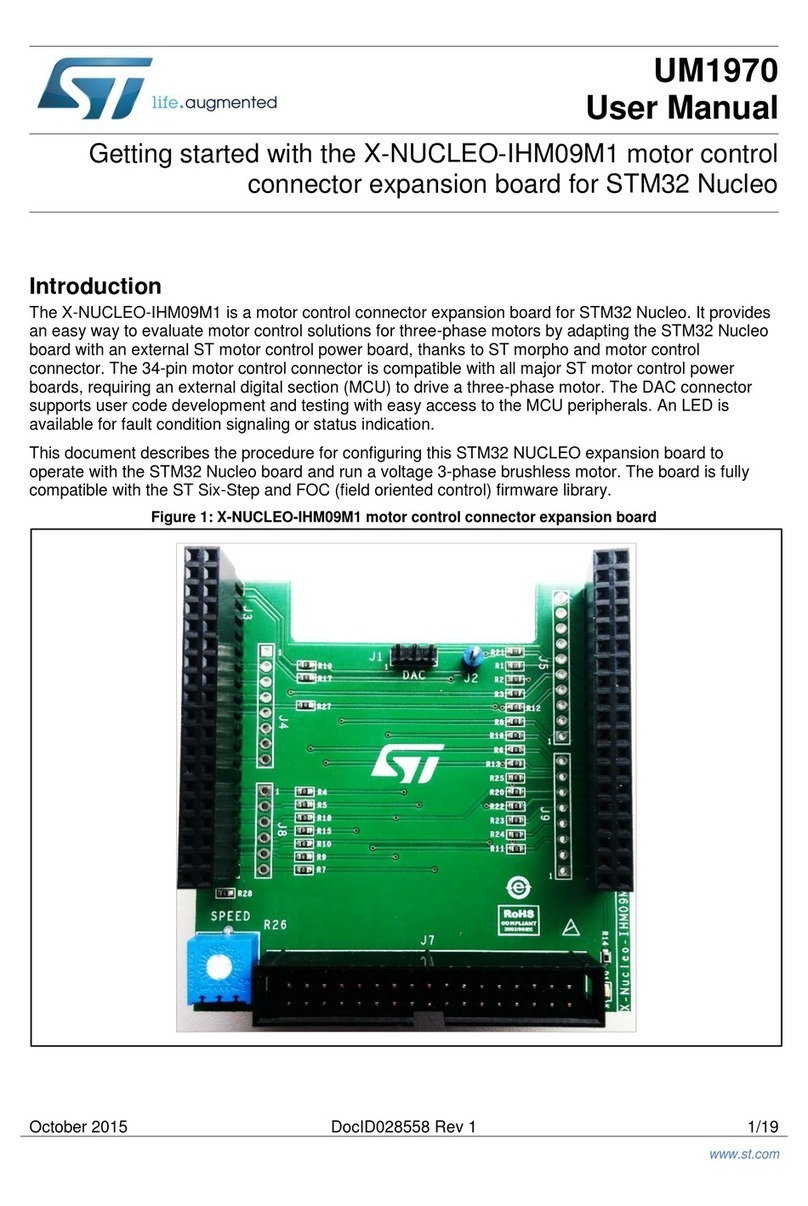

ST X-NUCLEO-IHM09M1 User manual

ST

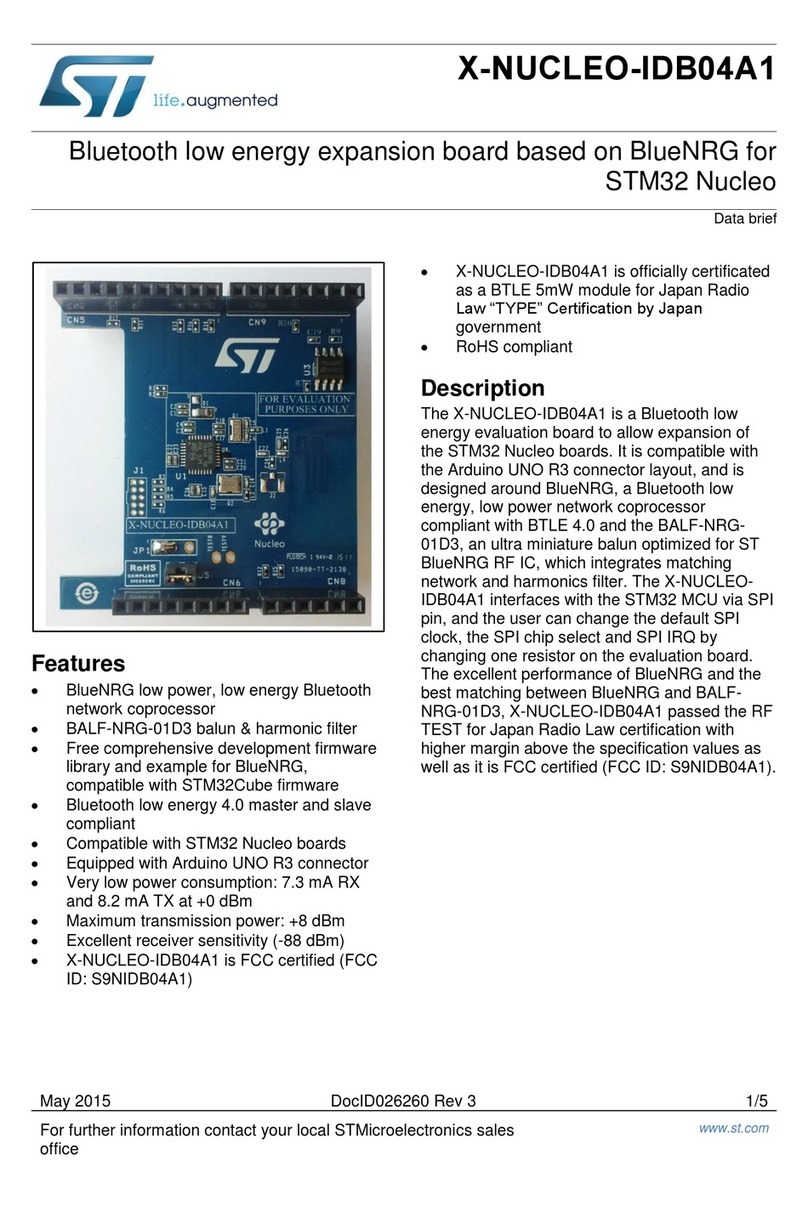

ST X-NUCLEO-IDB04A1 User manual

ST

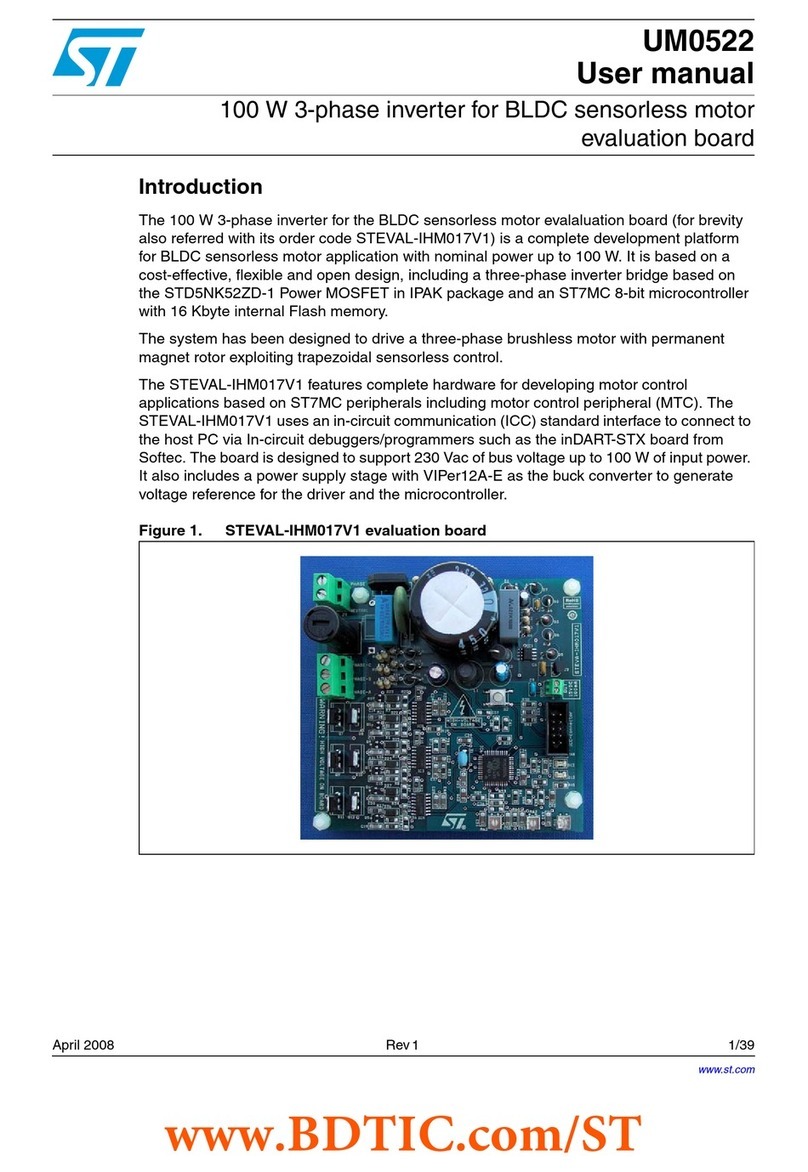

ST STEVAL-IHM017V1 User manual

ST

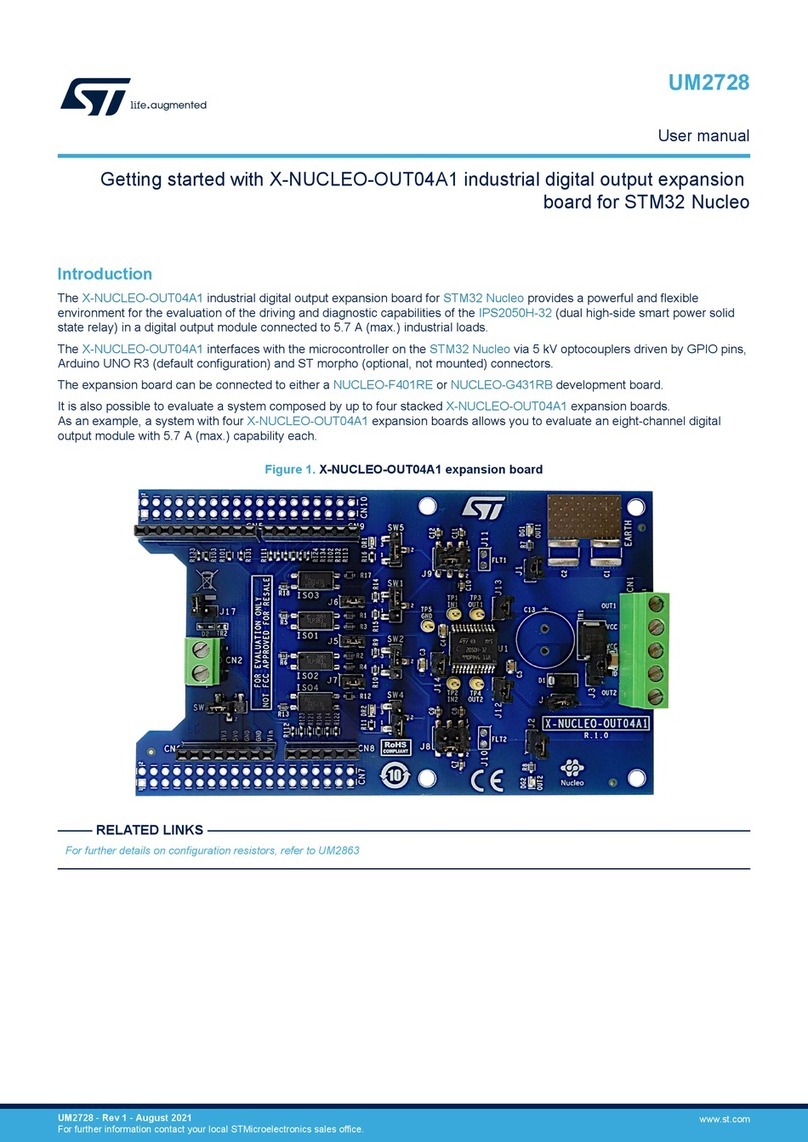

ST X-NUCLEO-OUT04A1 User manual

ST

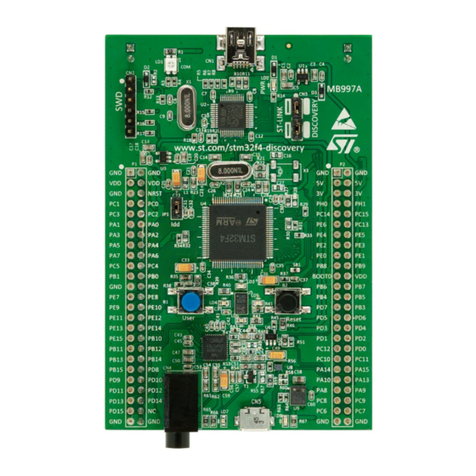

ST UM1472 User manual

ST

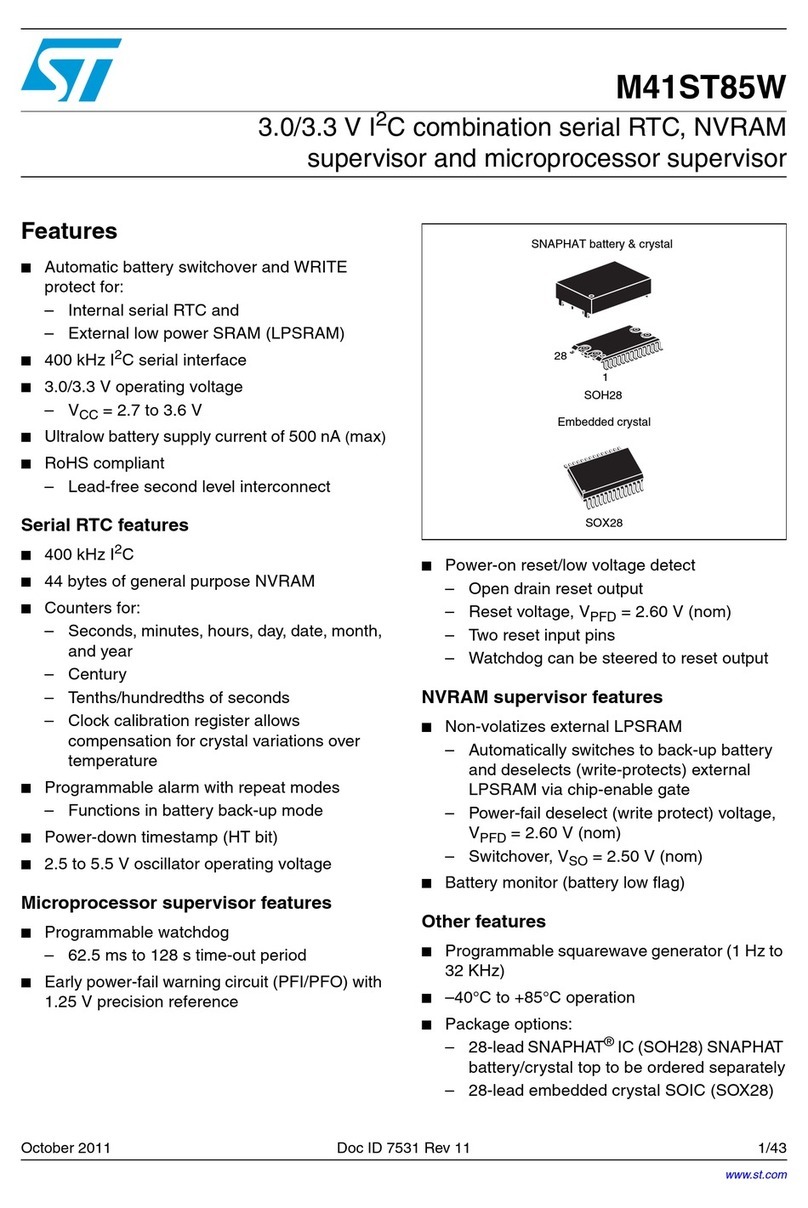

ST M41ST85W User manual

ST

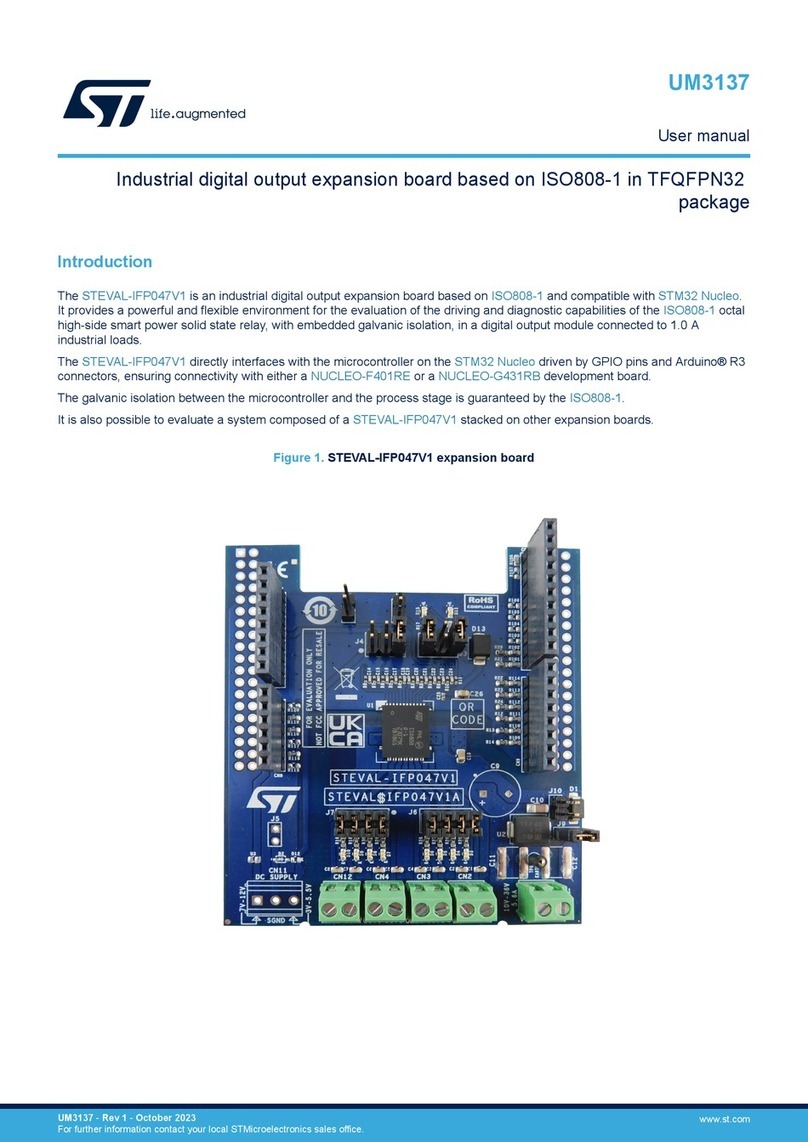

ST STEVAL-IFP047V1 User manual

ST

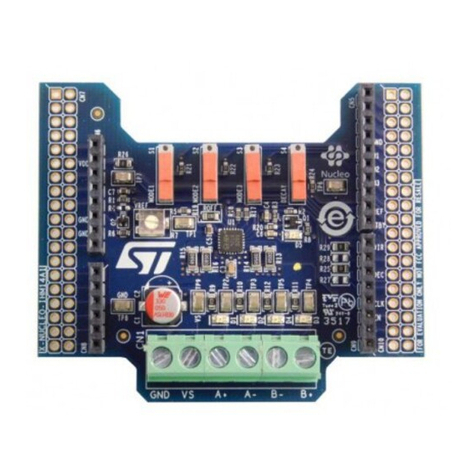

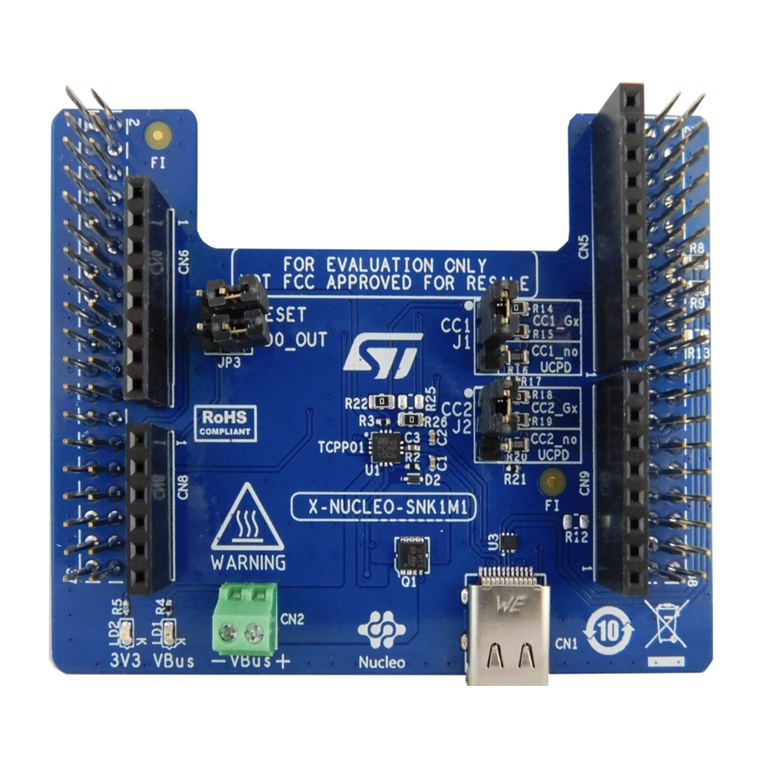

ST X-NUCLEO-SNK1M1 User manual

ST

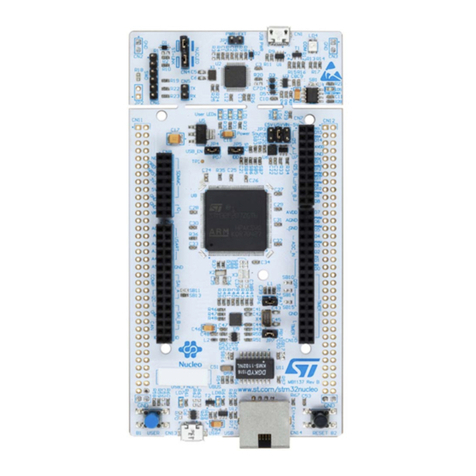

ST STM32 Nucleo User manual

ST

ST STM32 ODE User manual

ST

ST STM32W-RFCKIT User manual

ST

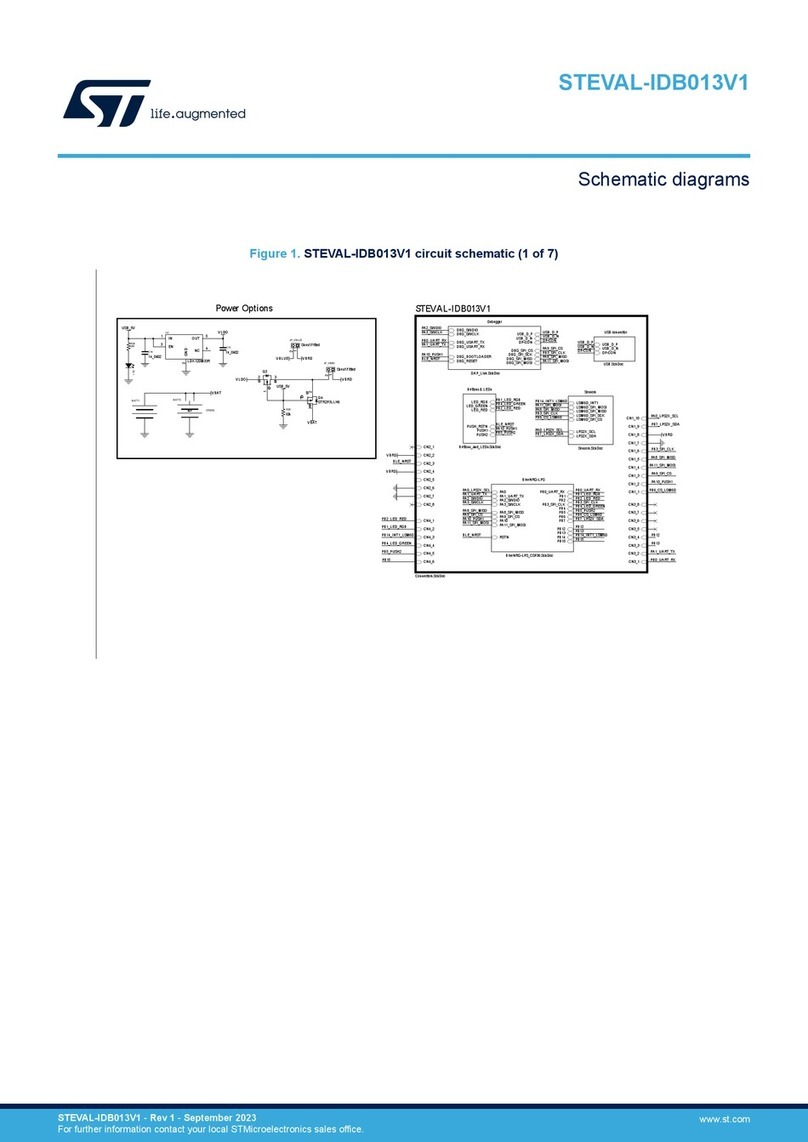

ST STEVAL-IDB013V1 Administrator Guide

ST

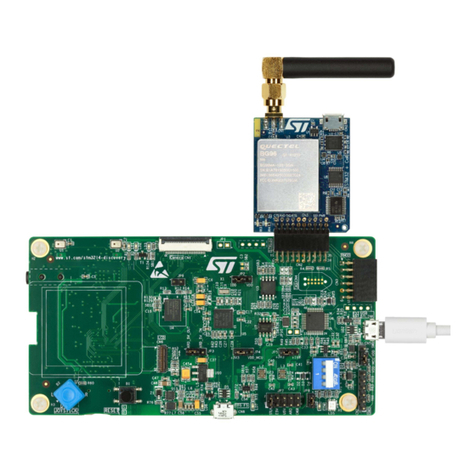

ST X-CUBE-CELLULAR User manual

ST

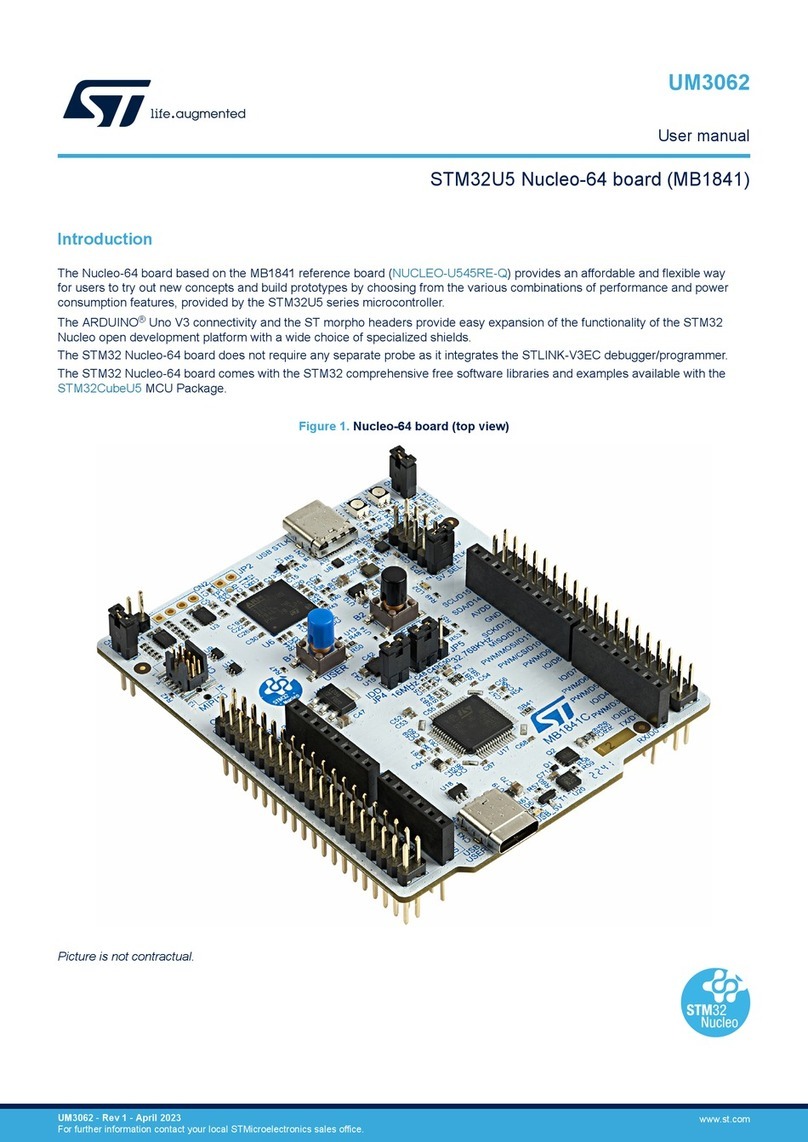

ST STM32U5 Nucleo-64 User manual

ST

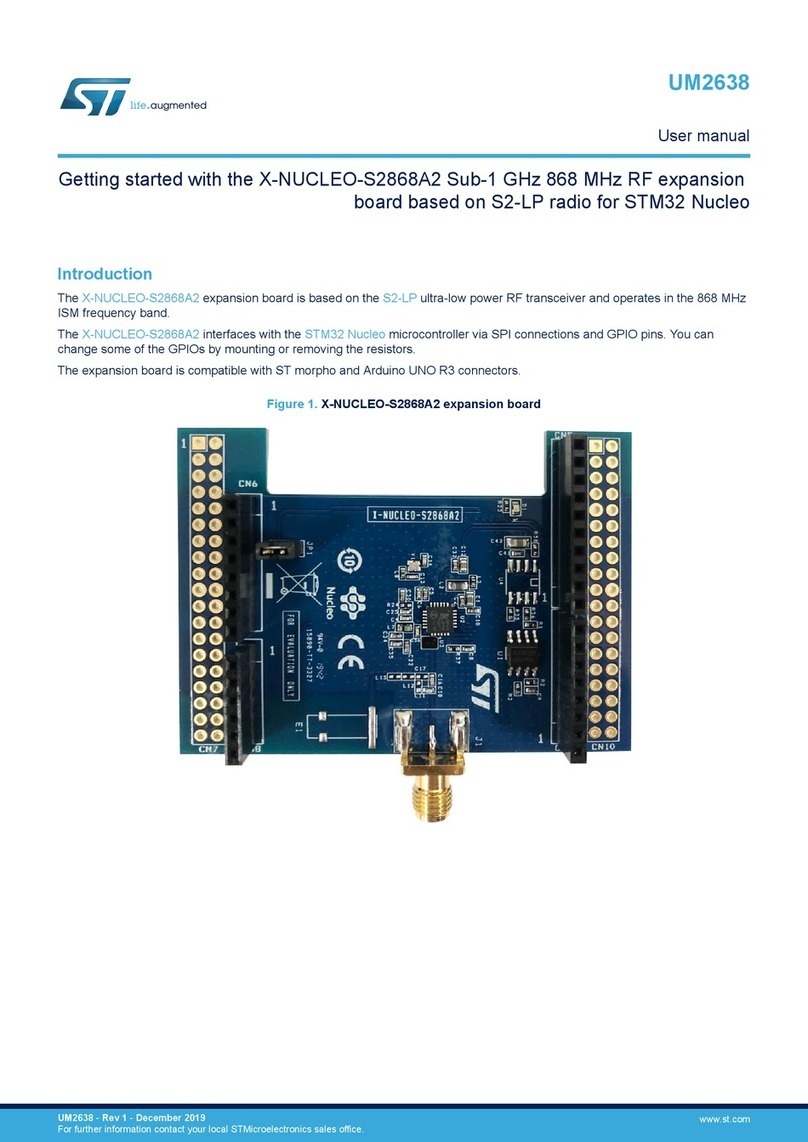

ST X-NUCLEO-S2868A2 User manual

ST

ST X-NUCLEO-OUT15A1 User manual

ST

ST X-NUCLEO-NFC01A1 User manual

ST

ST X-NUCLEO-IDW04A1 User manual

Popular Computer Hardware manuals by other brands

EMC2

EMC2 VNX Series Hardware Information Guide

Panasonic

Panasonic DV0PM20105 Operation manual

Mitsubishi Electric

Mitsubishi Electric Q81BD-J61BT11 user manual

Gigabyte

Gigabyte B660M DS3H AX DDR4 user manual

Raidon

Raidon iT2300 Quick installation guide

National Instruments

National Instruments PXI-8186 user manual

dbx

dbx Zone Pro 1260 user manual

Galaxy

Galaxy GHDX2-2430S-24F4D Installation and hardware reference manual

Intel

Intel AXXRMFBU4 Quick installation user's guide

Kontron

Kontron DIMM-PC/MD product manual

STEINWAY LYNGDORF

STEINWAY LYNGDORF SP-1 installation manual

Advantech

Advantech ASMB-935 Series user manual