ST SPC582B Series Installation and operating instructions

Other ST Microcontroller manuals

ST

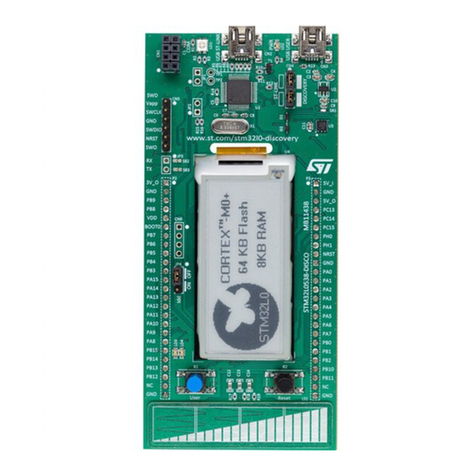

ST STM32F0DISCOVERY User manual

ST

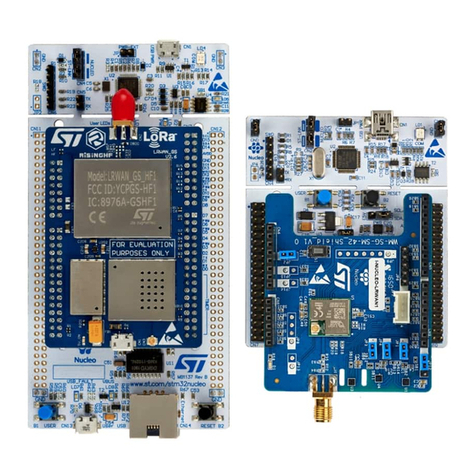

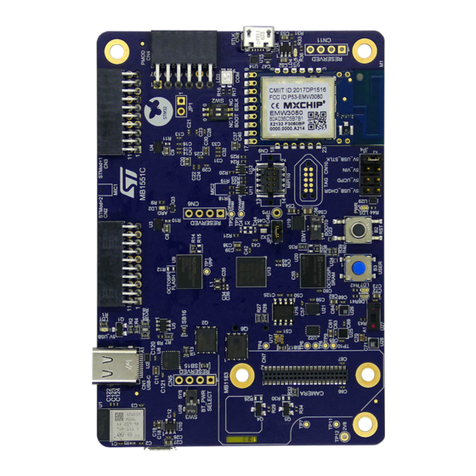

ST P-NUCLEO-LRWAN2 User manual

ST

ST STM32F030 User manual

ST

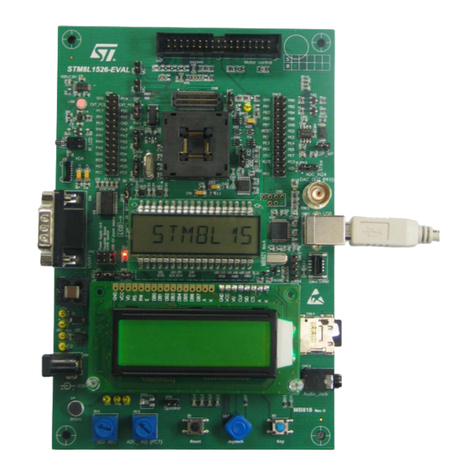

ST STM8L Installation and operating instructions

ST

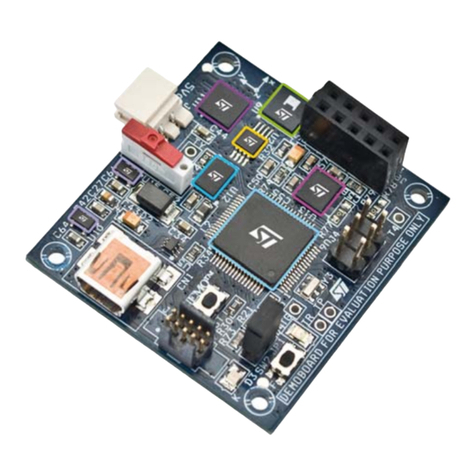

ST iNEMO STEVAL-MKI062V2 Series User manual

ST

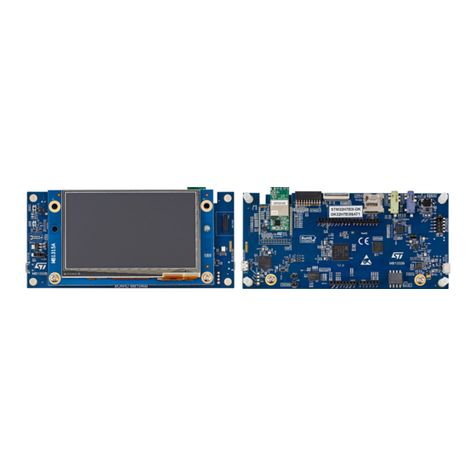

ST STM32H7B3I-DK User manual

ST

ST STM32 Nucleo Installation and operating instructions

ST

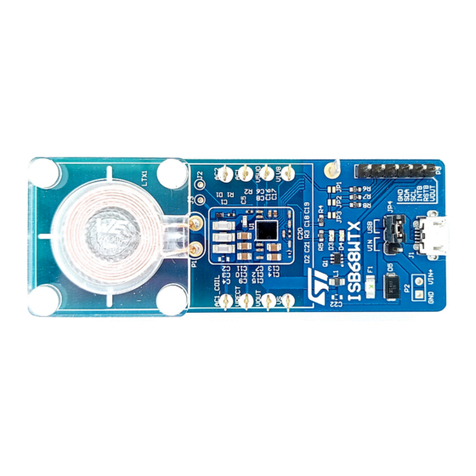

ST STEVAL-ISB68WTX User manual

ST

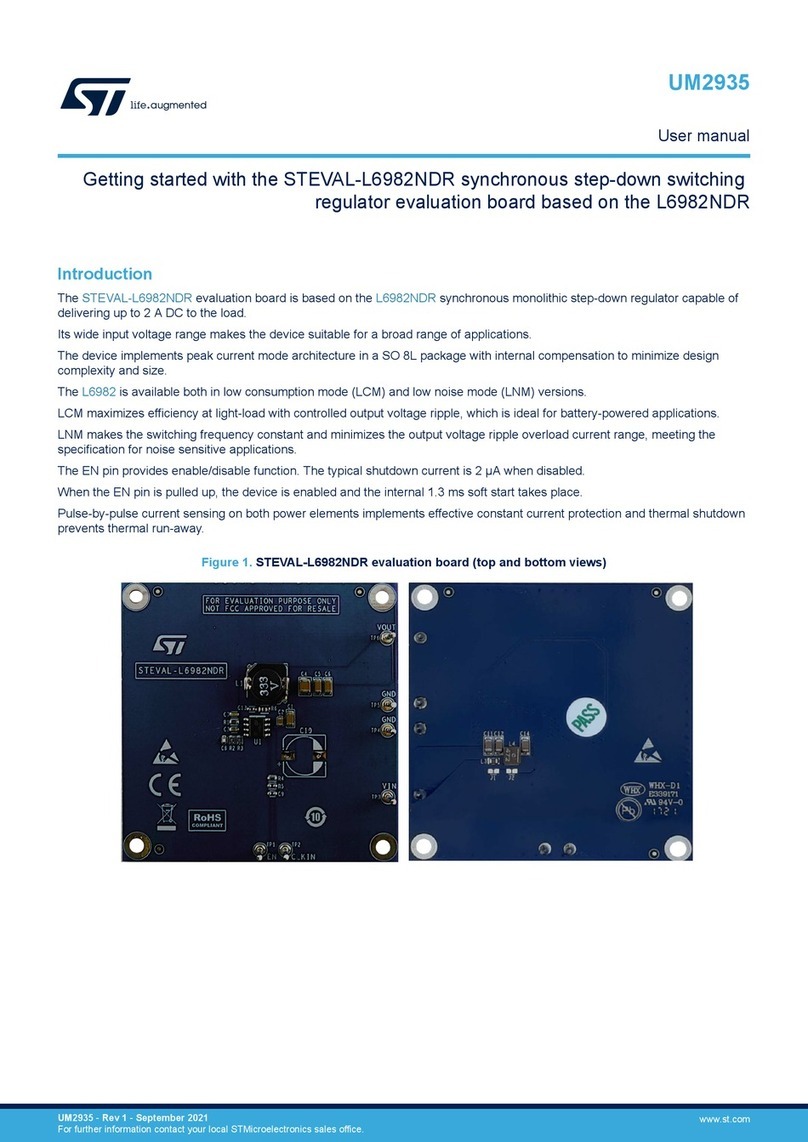

ST STEVAL-L6982NDR User manual

ST

ST STM32F40 Series User manual

ST

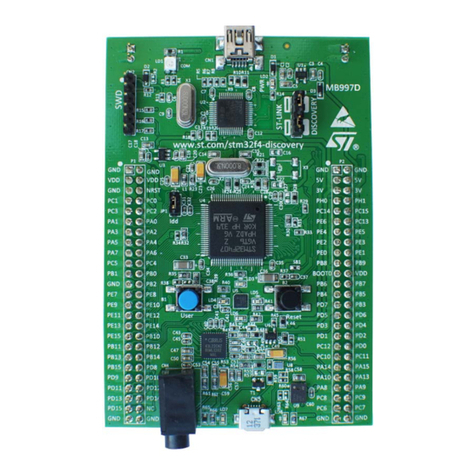

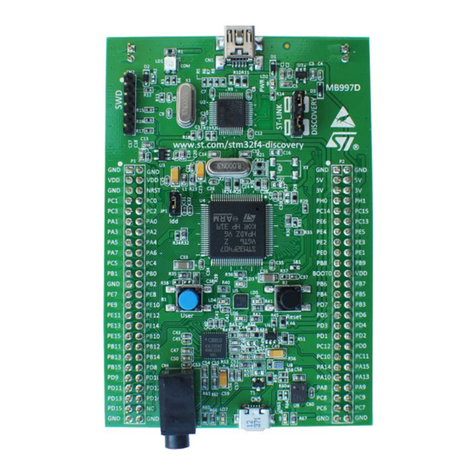

ST STM32F4DISCOVERY User manual

ST

ST STM32L0x3 User manual

ST

ST STM32 Series Installation and operating instructions

ST

ST STM32F423 Series User manual

ST

ST STM32U585 Series User manual

ST

ST STM32F10 Series Installation and operating instructions

ST

ST EVLKST8500GH868 User manual

ST

ST STM32F4DISCOVERY User manual

ST

ST STM32 Nucleo Installation and operating instructions

ST

ST STM32F0 Series Installation and operating instructions

Popular Microcontroller manuals by other brands

AMS

AMS AS7261 Demo Kit user guide

Novatek

Novatek NT6861 manual

Espressif Systems

Espressif Systems ESP8266 SDK AT Instruction Set

Nuvoton

Nuvoton ISD61S00 ChipCorder Design guide

STMicrolectronics

STMicrolectronics ST7 Assembler Linker user manual

Texas Instruments

Texas Instruments Chipcon CC2420DK user manual

Texas Instruments

Texas Instruments TMS320F2837 D Series Workshop Guide and Lab Manual

CYPRES

CYPRES CY14NVSRAMKIT-001 user guide

Texas Instruments

Texas Instruments INA-DUAL-2AMP-EVM user guide

Espressif Systems

Espressif Systems ESP8266EX Programming guide

Abov

Abov AC33M8128L user manual

Laird

Laird BL654PA user guide