Technologic Systems Date

Title:

Rev: Designer Sheet of

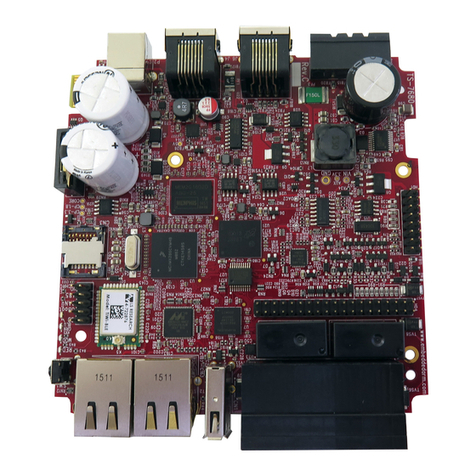

TS-7558 FPGA, JTAG Header

2

Pull-up and pull-down resistors

are 6 to 30K ohms

Set CONFIG_MODE to NONE

This allows all pins to be used

XP2-5 has:

9 blocks of 1Kx18 Block RAM

12 18x18 Multipliers

5K LUTS 2 PLLs

100 I/O with 144 pin package

"instant ON" = about 1.5 mS

input PLL clock = 10 MHz min

Power Supplies can be sequenced in any order

All I/O lines are tri-stated during power cycling

but must be monotonic

Page 37 of Data Sheet (Hot Socketing)

FPGA with 5000 LUTs

Interrupts

I2C

SPI_CS0#

I2S

SPI_CS1#

CLK+

CLK-

LED0

LED1

RLM

Console always is enabled

MODE1 and MODE2 states

are latched when

CPU_RESET# is deasserted

MODE1 and MODE2

have 4.7K resistor

pull-ups on WM-7550

JTAG

Header

26-pin

Mode 1 Mode 2 Boots from

1 1 NAND Flash

0 1

SD Card1 0

0 0

Off-board Flash

Off-board Flash

Use 680 ohm resistor

to GND to set low

Pin 54 Pin 138

(weak PD)

(weak PU)

TS-7500

TS-7550

WM-7551

TS-7552

TS-4500

1 1

1 1

00

1 0

Pin 71

0

7552 and 7553 FPGA pin 93 = MISO

Pin 37

1

1

1

1

0

00

1

1

1

0

Board ID bits

TS-7553 1 0 10

TS-7554 0 0 10

TS-7558 0 1 1

0

Hex

F

B

C

D

9

8

A

0

May 20, 2011

12A

54 and 71

biased low

must be

FPGA pins

139 must be

biased high

FPGA pin

40 IO

17 IO

27 IO

78 IO_CLK

90 IO

119 IO_CLK

65 IO

80 JTAG_DIN

81 JTAG_CLK

82 JTAG_DOUT

79 JTAG_TMS

3GND1

12 GND2

34 GND3

51 GND5

41 GND4

64 GND6

68 GND7

75 GND8

86 GND9

97 GND10

106 GND11

111 GND12

126 GND13

102

IO

104

IO

91

IO

72 IO

29

IO

115 IO

39 IO

28 IO_CLK

110 IO

1IO

15 IO

113 IO

13 OUT_CSSPIN

30 IO_CLK

129

IO

37 IO

2IO

32 IO

38 IO

9IN_CFG1

109 IO

7IN_PROGRAM#

69

IO

114 IO_CLK

116 IO_CLK

137 IO

141

IO

87

IO_CLK

88

IO_CLK

131

IO

47

IO

31

IO

43

IO

20

IO_INIT#

143

IO

5

IO

77

IO_CLK

138

IO

18

IO

6

IO

36

IO

11

IN_CSSPIS

46

IO

89

IO

122

IO

61

IO_CLK

19

IO

73

IO

132

IO

55

IO

35

IO

121

IO

52

IO

22

IO_CLK

44

IO

124

IO

16

IO_CCLK

142

IO

66

IO

8

IO_DONE

21

IO_CLK

53

IO

133

IO

96

IP

74

IO

99

IO

93

IO

58

IO_CLK 98

IO

144 IO

70

IO

45

IO

57

IO

120

IO_CLK

48

IO

23 VCC_AUX1

60 VCC_AUX2

85 VCC_AUX3

117 VCC_AUX4

24 VCC_INT1

59 VCC_INT2

84 VCC_INT3

118 VCC_INT4

100

IO

101

IO

107

IO

108

IO

10

IO

62

IO_CLK

103

IO

125

IO

71

IO

56

IO_CLK

54

IO

134

IO

130

IO

92

IO

127

IO

135 GND14

139 GND15

63 VCCO_4

42 VCCO_5

49 VCCO_5

33 VCCO_6

4VCCO_7

14 VCCO_7

83 VCC_JTAG

140 VCC_PLL_0

67 VCC_PLL_1

94 IO

50 IO

123 IO

25 TOE

26 CFG0

112 VCCO_1

128 VCCO_0

95 VCCO_2

105 VCCO_2

76 VCCO_3

136 VCCO_0

U8

LATTICE_XP2_144

R25

226 1%

1 2

RN2-A

4.7K

3

4

RN2-B

4.7K

R21

226 1%

R22

226 1%

R23

226 1%

RedGreen

31

42

LED1

DUAL_RTA_LED

12 SPI_MOSI

10 3.3V

8RXD

6TCK

4TDI

2TMS

11

SPI_CS#

9

SPI_MISO

7

MODE1/TXD

5

MODE2/DIO

3

GND

1

TDO

14 SPI_CLK 13

DIO_13

16 RESET# 15

DIO_15

18 DIO_18

20 DIO_20

22 DIO_22

24 DIO_24

26 DIO_26

17

DIO_17

19

DIO_19

21

DIO_21

23

DIO_23

25

DIO_25

HD1

HD_JTAG26_2009

FB4

R18

226 1%

1.2V

3.3V

JTAG_DOUT

JTAG_DIN

JTAG_CLK

JTAG_TMS

UN-RESET

WD_RESET#

NAND_CS#

NAND_WR#

NAND_ALE

NAND_CLE

NAND_BUSY#

NAND_WP#

FPGA_25MHZ

INT28

CPU_UART_TXD

CPU_UART_RXD

SPI_CLK

SPI_MOSI

SPI_MISO

RTC_SDA

RTC_SCL

GPIO_A0

GPIO_A1

SDA

SCL

GPIO_A3

GPIO_A15

GPIO_A16

GPIO_A17

JTAG_TMS

JTAG_DIN

GPIO_A28

GPIO_A29

ETH_LEFT_LED#

ETH_RIGHT_LED#

32KHZ

GPIO_A23

GPIO_A22

FPGA_CONFIG#

3.3V

NAND_D[0:7]

NAND_RD#

JTAG_DIN

MODE2

JTAG_TMS

JTAG_DOUT

3.3V

JTAG_CLK

CONSOLE_RXD CONSOLE_TXD

BOOT_SPI_CLK

BOOT_SPI_MOSI BOOT_SPI_CS#

BOOT_SPI_MISO

WD_RESET#

MODE2

CONSOLE_TXD

CONSOLE_RXD

BOOT_SPI_CS#

BOOT_SPI_MISO

BOOT_SPI_MOSI

BOOT_SPI_CLK

SCL

SDA

DIO_17

DIO_19

DIO_21

DIO_23DIO_24

DIO_22

DIO_20

DIO_18

EN_SD_POWER

PUSH_SW# SD_D0

SD_D1

SD_D2

SD_D3

SD_CMD

SD_CLK

NAND_D0

NAND_D1

NAND_D2

NAND_D3

NAND_D4

NAND_D5

NAND_D6

NAND_D7

EN_USB_POWER

CAN_TXD

CAN_RXD

485_TXEN

485_TXD

485_RXD

UART2_RXD

UART1_RXD

UART1_TXD

UART2_TXD

5V

EN_OUT1#

EN_OUT2#

EN_OUT3#

EN_OUT4#

ADC_CLK

ADC_DATA

ADC_CS#

ADC_MUX_A0

ADC_MUX_A1

ADC_MUX_A2

CL_CH2_EN

CL_CH3_EN

CL_CH4_EN

ADC_GAIN_2X

BUF_IN_1

BUF_IN_2

BUF_IN_3

BUF_IN_4

BUF_IN_5

BUF_IN_6

BUF_IN_7

BUF_IN_8

DIO_17

DIO_18

DIO_19

DIO_20

DIO_21

DIO_22

DIO_23

CL_CH1_EN

DIO_24

DIO_25

DIO_25