Chapter 1: Introduction R-Engine-D

Figure 1.1 Functional block diagram of the R-Engine-

The three 16-bit timers can be used to count or time external events, up to 10 MHz, 20MHz with the

R1100, or to generate non-repetitive or variable-duty-cycle waveforms as PWM outputs. The 32 PIO pins

from the Am186ER are multifunctional and user programmable.

A serial real time clock (DS1337, Dallas) is a low power clock/calendar with two time-of-day alarms and a

programmable square-wave output. A Dual UART (SC26C92) provides two channels of full-duplex

asynchronous receivers and transmitters; this combines with a single port available from the processor for a

total of three RS-232 serial ports. (This differs from most other core Engine controllers, offering 2 ports

through the processor.) The receivers are quadruple buffered to minimize the potential of receiver overrun

or to reduce interrupt overhead. The UARTs incorporate 9-bit mode for multi-processor communications.

Each UART also offers 7 TTL inputs and 8 TTL outputs. The PPI (82C55) provides an additional 24 user

programmable bi-directional I/Os. The PPI chip can interface to another processor module, or to an LCD

and keypad(s). The R-Engine-D also offers 14 high voltage sinking drivers or optional 16 high voltage

sourcing drivers, capable of sinking/sourcing 350mA at 50V per line.

The DAC (DAC7612) supports two channels of 12-bit, 0-4.095V analog voltage outputs capable of

sinking or sourcing 5 mA. Two of these are available to be installed on the R-Engine-D. A high-speed, up

to 300K samples per second, 8-channel, 12-bit parallel ADC (AD7852) can be installed. This ADC

includes sample-and-hold and precision internal reference, and has an input range of 0-5 V. The RE also

supports a 4-channel, high-speed parallel DAC* (DA7625, 0-2.5V, 200KHz).

An optional 16-bit serial ADC (ADS8344, 100KHz) successive approximation converter, offering 8 single-

ended input or 4-differential inputs, is also available.

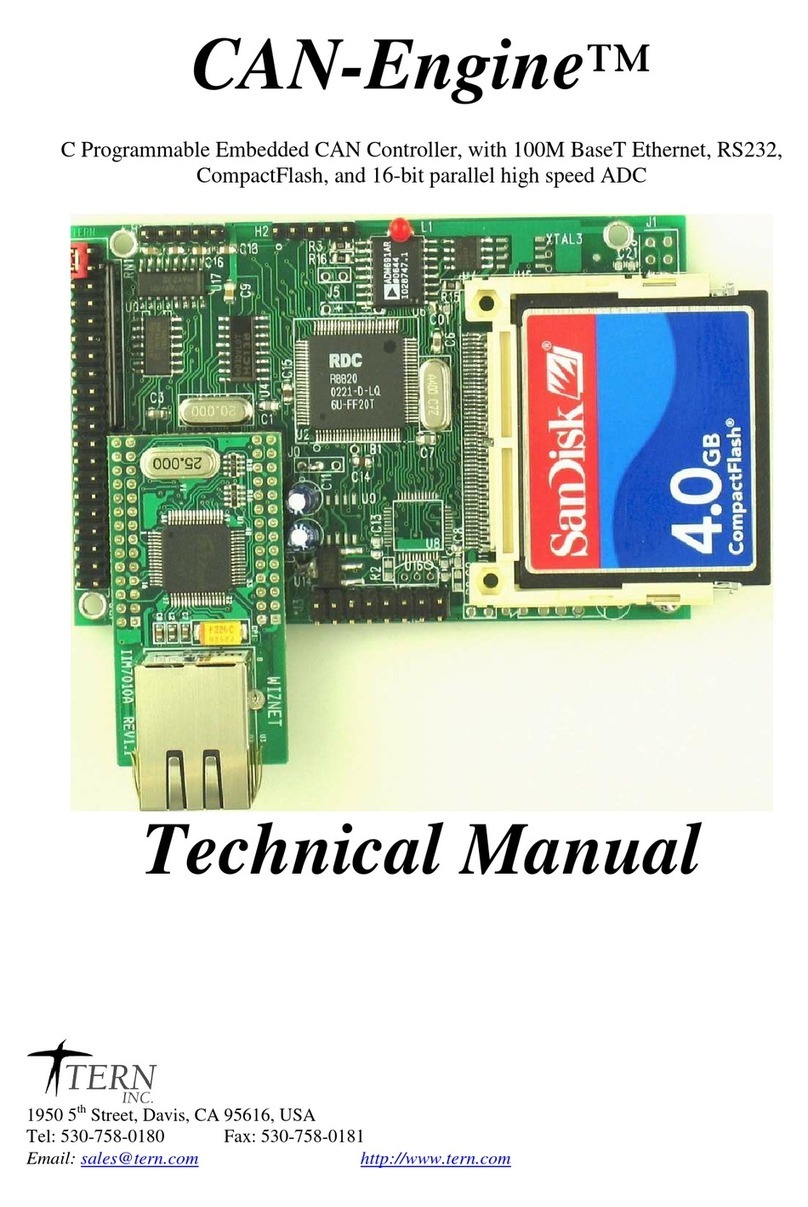

A 50-pin CompactFlash receptacle can be installed to allow access to mass storage CompactFlash cards

(up to 1GB). Users can easily add mass data storage to their embedded application. FAT File system

support is available.

An Ethernet LAN controller (CS8900) can be installed to provide network connectivity. A RJ45 8-pin

connector is used to connect to a 10-baseT Ethernet network. Software libraries are available.

1.3 Features

•Dimensions: 3.9 x 3.6 inches

•Temperature: -40°C to +80°C

•40 MHz, 16-bit CPU (Am186ER), Intel 80x86 compatible, OR

•80 MHz, 16-bit CPU (R1100)

•32KB internal RAM, Am186ER ONLY

•Easy to program in C/C++

•Power consumption: 160 mA

•Power-save mode: 20 mA

•Standby mode: 50µA

•Power input: + 9V to +12V unregulated DC with linear regulator (standard)

+9V to +30V unregulated DC with optional switching regulator

•Up to 256 KW 16-bit SRAM, 256 KW 16-bit Flash *

•8-channel 300 KHz parallel 12-bit ADC (AD7852) with 0-5V analog input*

•4-channel 200 KHz parallel 12-bit DAC (DA7625) with 0-2.5V analog output*

•4-channels serial 12-bit DAC (DAC7612), 7us settling time*

•8-channel serial 16-bit ADC (ADS8344) with 0-5V analog input*

•16-bit external data bus expansion port

•10-baseT ethenet network connectivity with LAN controller (CS8900)

1-2