Table of Contents

1 Features............................................................................1

2 Applications..................................................................... 1

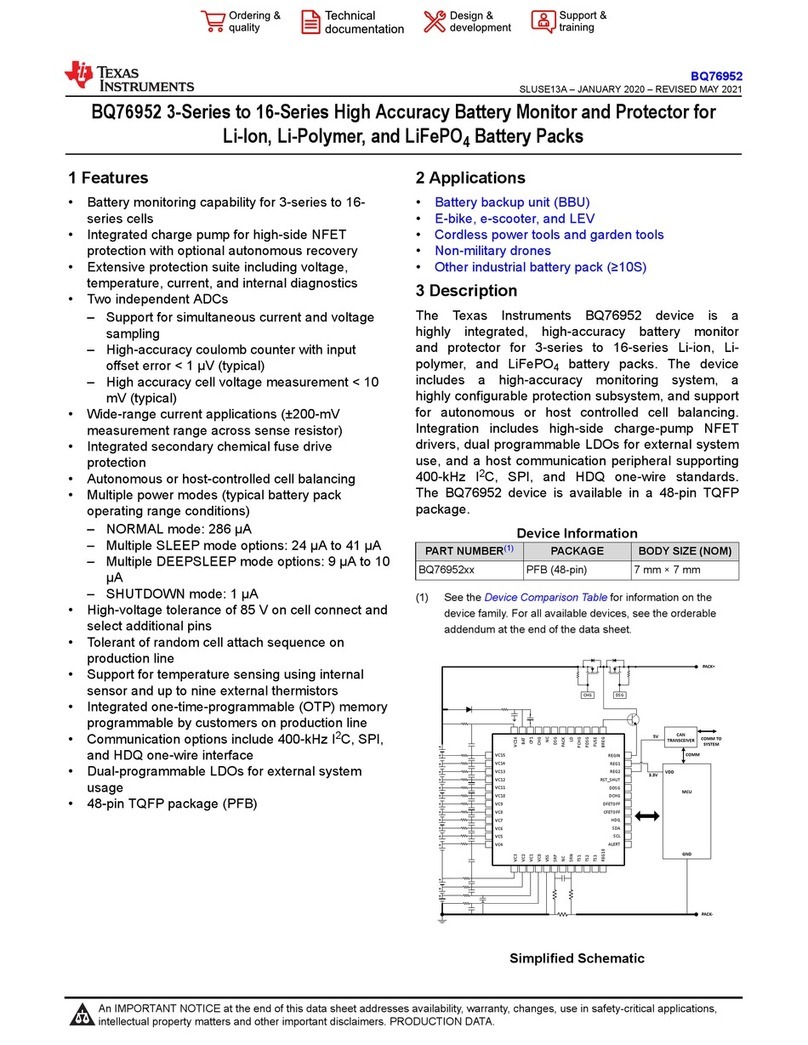

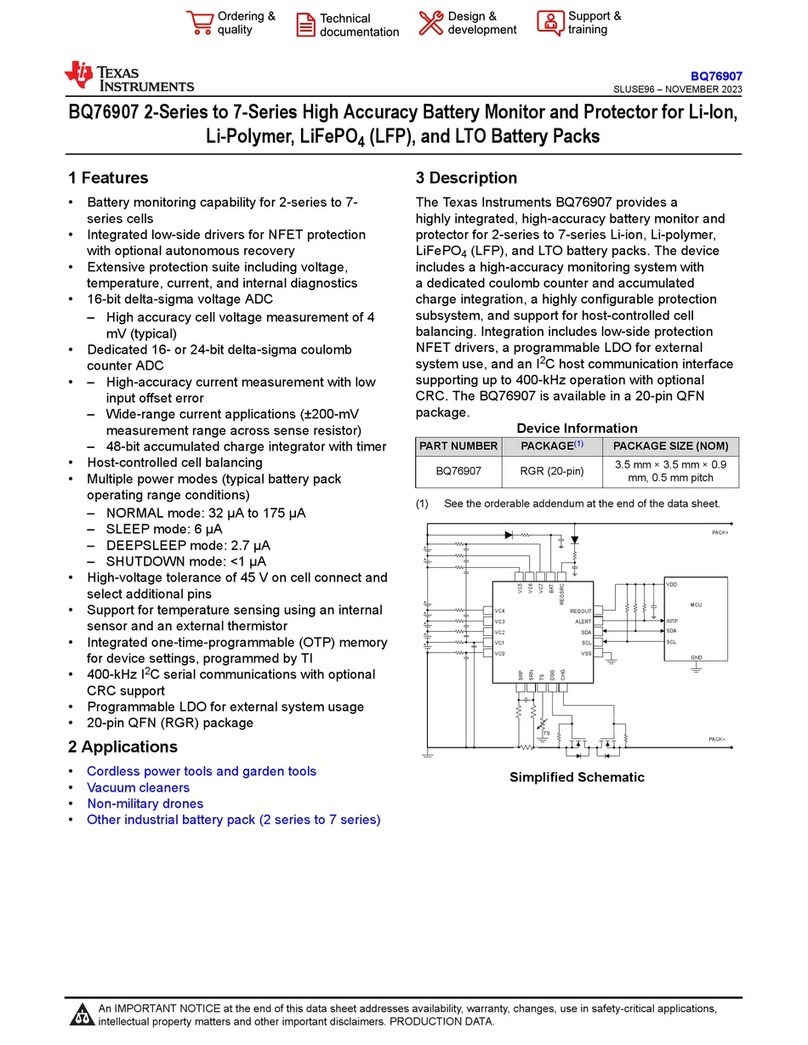

3 Description.......................................................................1

4 Device Comparison Table...............................................3

5 Pin Configuration and Functions...................................3

6 Specifications.................................................................. 5

6.1 Absolute Maximum Ratings........................................ 5

6.2 ESD Ratings............................................................... 5

6.3 Recommended Operating Conditions.........................6

6.4 Thermal Information....................................................7

6.5 Supply Current............................................................ 7

6.6 Digital I/O.................................................................... 7

6.7 REGOUT LDO............................................................ 8

6.8 Voltage References.....................................................8

6.9 Coulomb Counter........................................................9

6.10 Coulomb Counter Digital Filter..................................9

6.11 Current Wake Detector............................................10

6.12 Analog-to-Digital Converter.....................................13

6.13 Cell Balancing......................................................... 15

6.14 Internal Temperature Sensor.................................. 15

6.15 Thermistor Measurement........................................15

6.16 Hardware Overtemperature Detector......................16

6.17 Internal Oscillator.................................................... 16

6.18 Charge and Discharge FET Drivers........................16

6.19 Comparator-Based Protection Subsystem..............17

6.20 Timing Requirements—I2C Interface, 100-kHz

Mode........................................................................... 19

6.21 Timing Requirements—I2C Interface, 400-kHz

Mode........................................................................... 20

6.22 Timing Diagram.......................................................20

6.23 Typical Characteristics............................................ 21

7 Detailed Description......................................................26

7.1 Overview................................................................... 26

7.2 Functional Block Diagram......................................... 26

7.3 Device Configuration.................................................27

7.3.1 Commands and Subcommands......................... 27

7.3.2 Configuration Using OTP or Registers .............. 27

7.3.3 Device Security.................................................. 27

7.4 Device Hardware Features....................................... 27

7.4.1 Voltage ADC.......................................................27

7.4.2 Coulomb Counter and Digital Filters.................. 28

7.4.3 Protection FET Drivers....................................... 28

7.4.4 Voltage References............................................ 29

7.4.5 Multiplexer.......................................................... 29

7.4.6 LDOs.................................................................. 29

7.4.7 Standalone Versus Host Interface......................29

7.4.8 ALERT Pin Operation.........................................30

7.4.9 Low Frequency Oscillator...................................30

7.4.10 I2C Serial Communications Interface............... 30

7.5 Measurement Subsystem......................................... 32

7.5.1 Voltage Measurement........................................ 32

7.5.2 Current Measurement and Charge Integration...33

7.5.3 Internal Temperature Measurement................... 34

7.5.4 Thermistor Temperature Measurement.............. 34

7.5.5 Factory Trim and Calibration.............................. 34

7.6 Protection Subsystem............................................... 35

7.6.1 Protections Overview......................................... 35

7.6.2 Primary Protections............................................ 35

7.6.3 CHG Detector.....................................................35

7.6.4 Cell Open-Wire Protection..................................36

7.6.5 Diagnostic Checks..............................................36

7.7 Cell Balancing........................................................... 37

7.8 Device Operational Modes........................................37

7.8.1 Overview of Operational Modes......................... 37

7.8.2 NORMAL Mode.................................................. 38

7.8.3 SLEEP Mode......................................................38

7.8.4 DEEPSLEEP Mode............................................ 39

7.8.5 SHUTDOWN Mode............................................ 39

7.8.6 CONFIG_UPDATE Mode................................... 40

8 Application and Implementation.................................. 41

8.1 Application Information............................................. 41

8.2 Typical Application.................................................... 41

8.2.1 Design Requirements.........................................44

8.2.2 Detailed Design Procedure................................ 45

8.2.3 Application Performance Plot............................. 46

8.2.4 Random Cell Connection Support......................46

8.2.5 Startup Timing.................................................... 47

8.2.6 FET Driver Turn-Off............................................48

8.2.7 Usage of Unused Pins........................................51

8.3 Power Supply Recommendations.............................51

8.4 Layout....................................................................... 52

8.4.1 Layout Guidelines...............................................52

8.4.2 Layout Example..................................................52

9 Device and Documentation Support............................54

9.1 Documentation Support............................................ 54

9.1.1 Related Documentation......................................54

9.2 Receiving Notification of Documentation Updates....54

9.3 Support Resources................................................... 54

9.4 Trademarks...............................................................54

9.5 Electrostatic Discharge Caution................................54

9.6 Glossary....................................................................54

10 Revision History.......................................................... 54

11 Mechanical, Packaging, and Orderable

Information.................................................................... 55

BQ76905

SLUSE97 – NOVEMBER 2023 www.ti.com

2Submit Document Feedback Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: BQ76905