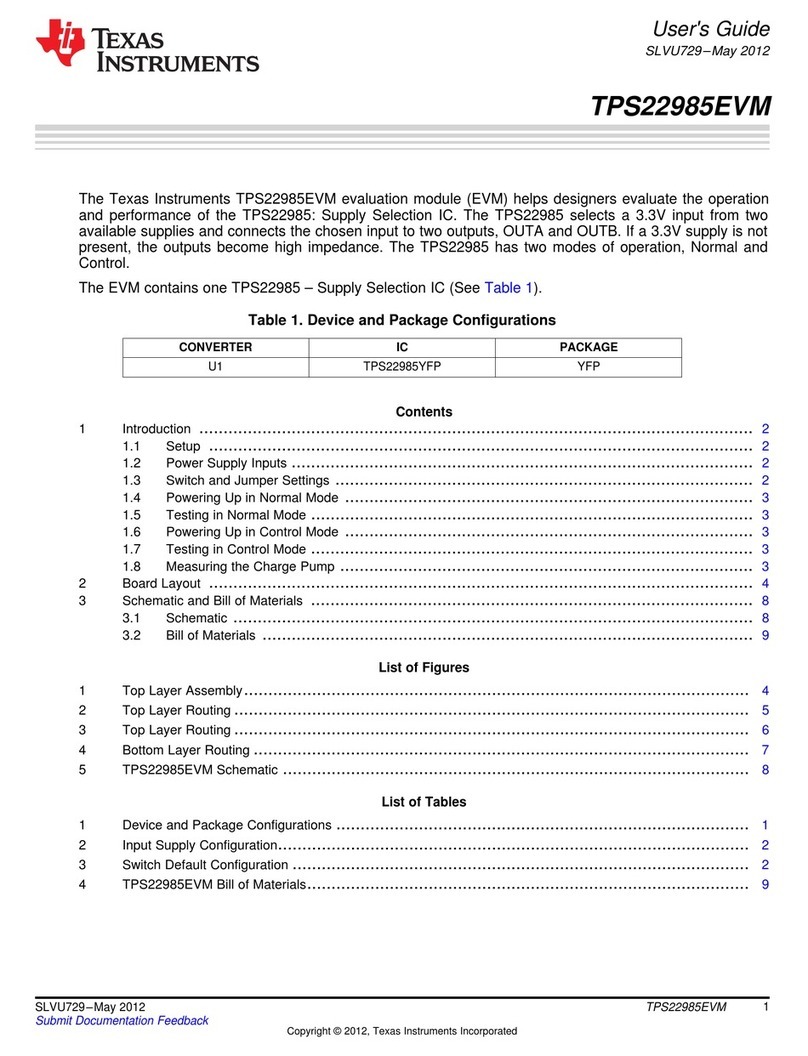

3.1.2 Jumper Options

3.1.3 ADS1610EVM OTR LED

3.1.4 ADS1610 Reset

3.1.5 Interrupt Source

3.1.6 Base Address and Chip Select

Digital Interface

Table 3. Switch Function Control, SW1 (continued)

Switch, SW1

Position Function ON(LO) OFF(HI)

7 Not used8 Not used

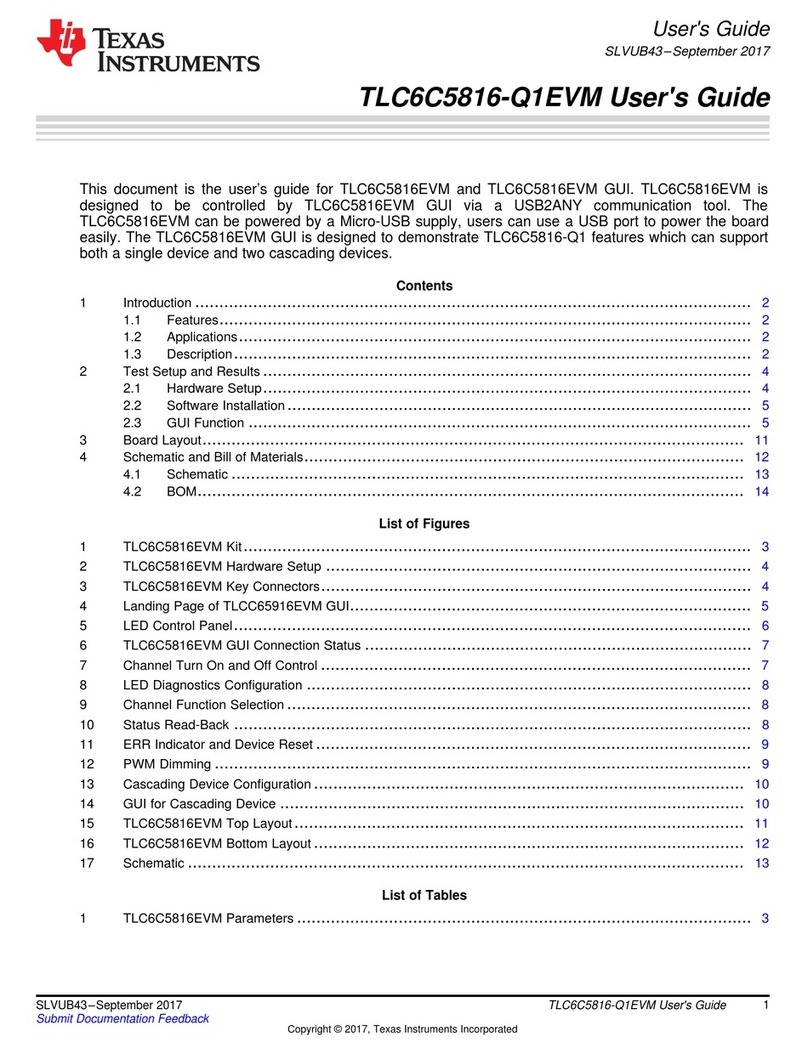

Four jumpers are associated with the digital control section; their functions are detailed in Table 4 .

Table 4. Digital Jumper

Reference 1-2 2-3 DescriptionDesignator

W20 Installed Not installed Set SYNCB to output of combinatory logicNot installed Installed

(1)

Set SYNCB to user reset switchW23 Installed

(1)

Not installed Set DRDY_OUT to DRDY of ADS1610Not installed Installed Set DRDY_OUT to inverted DRDY of ADS1610.J19 2-1 Installed

(1)

N/A Set U16A pin 2 to LOW. Used in EVM address decoding logic.J19 3-4 Installed

(1)

N/A Set U17A pin 2 to LOW. Used in board address decoding logic.

(1)

Factory installed

When the analog input exceeds the positive full-scale value or goes below negative full-scale value ofVREF, the Out of Range (OTR) signal goes HIGH and remain high while the signal is out-of-range. Whenthis condition occurs, LED1 illuminates. To clear the LED, flip-flop U13 must be reset. Depending on whichposition W20 is set to, the LED can be reset manually via SW2 or through programming by issuing a WRoperation from the host processor. The factory-set condition of W20 is a short across pins 2-3. This allowsthe user to manually reset the LED and reset the ADS1610.

The ADS1610 can be asynchronously reset when the SYNC pin is driven low. In reset, all the digitalcircuits are cleared, the data bus is LOW, and DRDY is HIGH. The ADS1610 can be reset in two ways,using an manual reset via SW1 or by programming from the host system. If W20 pins 1-2 are shorted, theSYNC signal must be generated by the host system. If W20 pins 2-3 are shorted, then the SYNC signal tothe ADS1610 is generated manually by momentarily depressing switch SW2.

Some microprocessors only recognize falling edge interrupts; others only recognize rising edge interrupts.Some can be programmed to recognize either. W23 can be set by the user to select either rising edge orfalling edge. If a jumper is across pins 1 and 2, DRDY is applied to DRDY_OUT pin. If jumper short isacross pins 2 and 3, an inverted version of DRDY is applied to DRDY_OUT pin.

The EVM can be mapped into a memory location by setting a base address. The EVM has four possiblebase addresses. The base address is set by J19. When the logic state of the two external address signalsmatches the logic state set up by the two jumpers on J19 and the access is valid memory access, theEVM generates a CS signal for the ADC. This then can be further qualified as a read cycle or a write( RESET) cycle. An installed jumper is equivalent to logic 0 on the corresponding address line. Anuninstalled jumper is equivalent to logic 1 on the corresponding address line.

SLAU180A – May 2006 – Revised August 2006 ADS1610EVM 5Submit Documentation Feedback