www.ti.com

List of Figures

1 TPS53317AEVM-726 Schematic.......................................................................................... 7

2 Tip and Barrel Measurement for VOUT Ripple .......................................................................... 8

3 TPS53317AEVM-726 Recommended Test Set Up ..................................................................... 9

4 Efficiency .................................................................................................................... 13

5 Load Regulation............................................................................................................ 13

6 Output Load 0-A to 3-A Transient (1.2-V VIN, 0.6-V VOUT, PWM Mode, fSW = 600 kHz) ........................... 14

7 Output Load 0-A to 3-A Transient with Droop (1.2-V VIN, 0.6-V VOUT, PWM Mode, fSW = 600 kHz) ............. 14

8 Output Ripple (1.2-V VIN, 0.6-V VOUT, 3-A IOUT, fSW = 600 kHz)........................................................ 15

9 Output Ripple (1.2-V VIN, 0.6-V VOUT, 3-A IOUT, fSW = 1 MHz) ......................................................... 15

10 Switching Node (1.2-V VIN, 0.6-V VOUT, 3-A IOUT, fSW = 600 kHz)...................................................... 16

11 Switching Node (1.2-V VIN, 0.6-V VOUT, 3-A IOUT, fSW = 1 MHz)........................................................ 16

12 Turn-On Waveform (1.2-V VIN, 0.6-V VOUT, 3-A IOUT)................................................................... 17

13 Turn-Off Waveform (1.2-V VIN, 0.6-V VOUT, 3-A IOUT).................................................................. 17

14 Pre-Bias Turn-On Waveform (1.2-V VIN, 0.6-V VOUT, 0-A IOUT, 0.3-V Pre-Bias)..................................... 18

15 Loop Gain (1.2-V VIN, 0.6-V VOUT, 3-A IOUT, PWM Mode, fSW = 600 kHz, Non-Droop).............................. 18

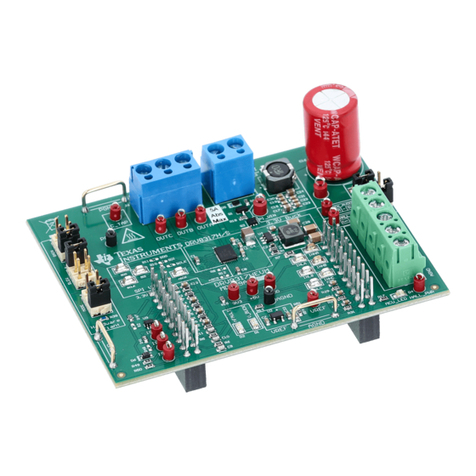

16 Thermal Image (1.2-V VIN, 0.6-V VOUT, 6-A IOUT, PWM Mode, fSW = 600 kHz)....................................... 19

17 TPS53317AEVM-726 Top Layer Assembly Drawing (Top View).................................................... 20

18 TPS53317AEVM-726 Bottom Assembly Drawing (Bottom View).................................................... 20

19 TPS53317AEVM-726 Top Copper (Top View)......................................................................... 21

20 TPS53317AEVM-726 Layer 2 (Top View) .............................................................................. 21

21 TPS53317AEVM-726 Layer 3 (Top View) .............................................................................. 22

22 TPS53317AEVM-726 Bottom Layer (Top View) ....................................................................... 22

3

SLUUBD2–November 2015 List of Figures

Submit Documentation Feedback Copyright © 2015, Texas Instruments Incorporated