Figure 5-4. Input Current vs Power, VDD-VEE Loading Only....................................................................................................15

Figure 5-5. Start-up 1: VIN=24 V, IVDD-VEE = 0 mA.................................................................................................................... 15

Figure 5-6. Start-up 2: VIN=24 V, IVDD-VEE = 80 mA.................................................................................................................. 16

Figure 5-7. Start-up 3: VIN=24 V, IVDD-VEE = 80 mA.................................................................................................................. 16

Figure 5-8. Start-up 4: VIN=24 V, IISO = 80 mA........................................................................................................................17

Figure 5-9. Inrush Current: VIN=24 V, IVDD-VEE = 80 mA...........................................................................................................17

Figure 5-10. Inrush Current: VIN=24 V, IVDD-VEE = 80 mA.........................................................................................................18

Figure 5-11. VDDAC=300 mV, VEEAC=108 mV, IVDD=80 mA, IVEE=10 mA................................................................................ 18

Figure 5-12. AC Ripple: VIN=24 V, IVDD=80 mA, IVEE=10 mA, FSSM = 5 kHz...................................................................... 19

Figure 5-13. AC Ripple: VIN=24 V, IVDD=80 mA, IVEE=10 mA, FMOD=45 kHz..................................................................... 19

Figure 5-14. AC Ripple: VIN=24 V, IVDD=80 mA, FSW(PRI)=12.95 kHz, ............................................................................... 20

Figure 5-15. AC Ripple: VIN=24 V, IVDD=80 mA, FBURST=1 MHz, ....................................................................................... 20

Figure 5-16. ENA to /PG Delay, 3.9 ms, IVDD-VEE = 80 mA........................................................................................................21

Figure 5-17. RLIM: VIN=24 V, IVDD-VEE = 0 mA......................................................................................................................... 21

Figure 5-18. RLIM: VIN=24 V, IVDD-VEE=100 mA....................................................................................................................... 22

Figure 5-19. RLIM: VIN=24 V, IVDD-VEE = 100 mA..................................................................................................................... 22

Figure 5-20. Output UVLO, PVDD=0 mW, PVEE = 73 mW...................................................................................................... 23

Figure 5-21. VEE OVP, VIN=24 V, PVDD=247 mW, PVEE = 0 mW..........................................................................................24

Figure 5-22. Normal Start, VIN=24 V, PVDD=247 mW, PVEE = 53 mW...................................................................................24

Figure 5-23. Shutdown by VIN Removal: VINOFF=18 V, IVDD-VEE = 80 mA............................................................................... 25

Figure 5-24. Shutdown by EN Low: VIN=24 V, IVDD-VEE = 80 mA............................................................................................. 25

Figure 5-25. Steady State, PMAX=2 W....................................................................................................................................... 26

Figure 5-26. Rated Power, P=1.65 W........................................................................................................................................ 26

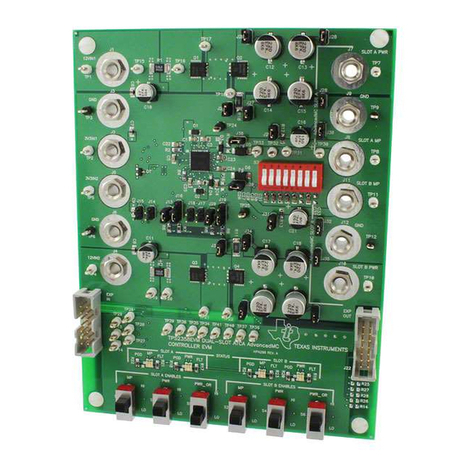

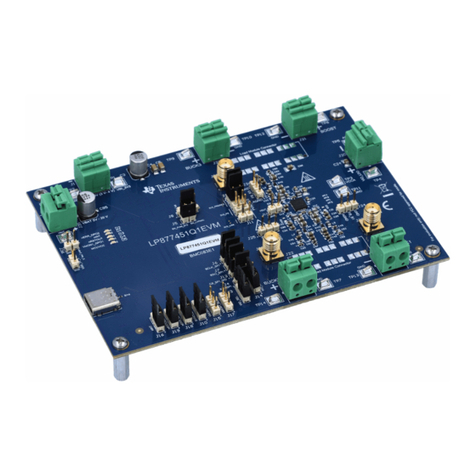

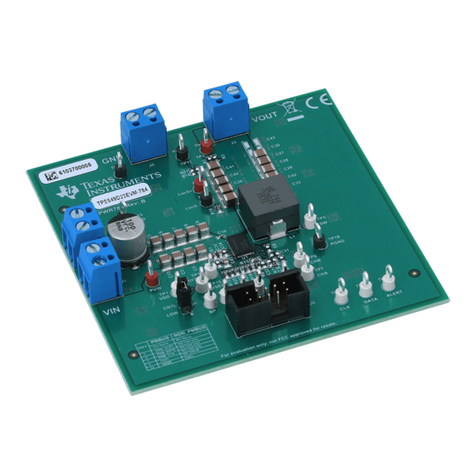

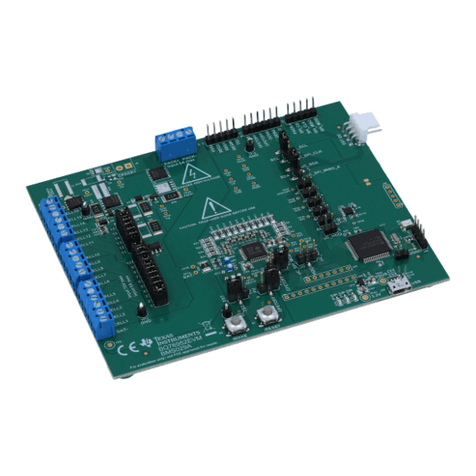

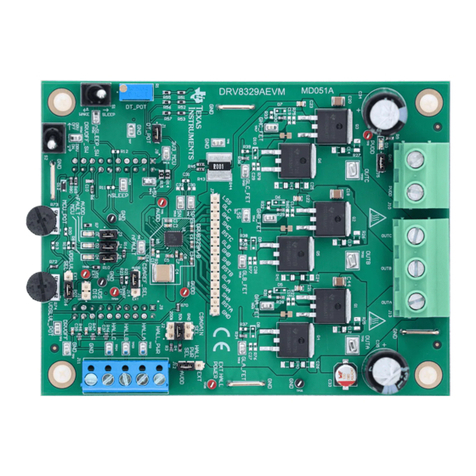

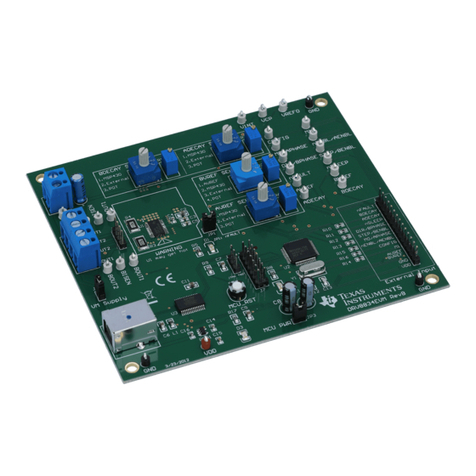

Figure 6-1. UCC14240EVM-052, Fully Assembled 3D Top View.............................................................................................. 27

Figure 6-2. UCC14240EVM-052, Fully Assembled 3D Bottom View.........................................................................................27

Figure 6-3. UCC14240EVM-052, 3D Angle View...................................................................................................................... 27

Figure 6-4. UCC14240EVM-052, PCB Top Layer, Assembly.................................................................................................... 28

Figure 6-5. UCC14240EVM-052, GND Layer 2 (same as layer 3)............................................................................................28

Figure 6-6. UCC14240EVM-052, GND Layer 3 (same as layer 2)............................................................................................29

Figure 6-7. UCC14240EVM-052, PCB Bottom Layer, Assembly (mirrored view)..................................................................... 29

List of Tables

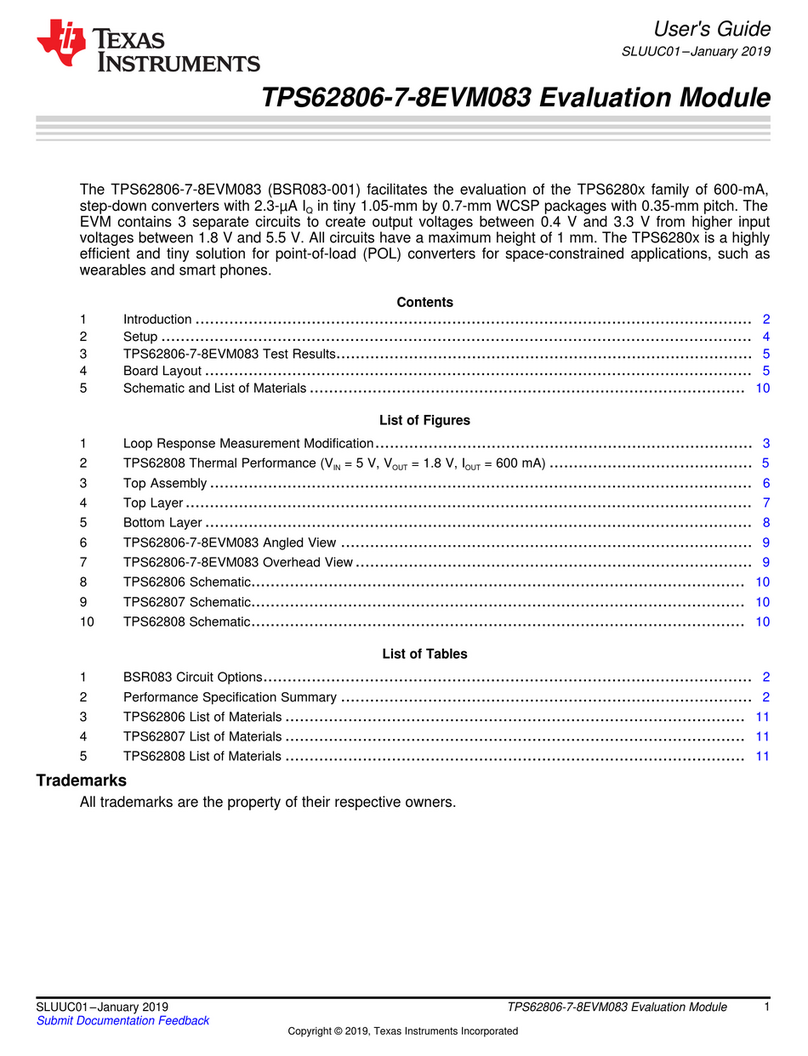

Table 1-1. UCC1424x-Q1 Version Differences............................................................................................................................ 3

Table 1-2. Pin Functions.............................................................................................................................................................. 4

Table 2-1. EVM Electrical Specifications..................................................................................................................................... 6

Table 4-1. Input, Output, Test Point (I/O/TP) Description...........................................................................................................10

Table 5-1. Efficiency Test Data (VIN = 21 V) .............................................................................................................................12

Table 5-2. Efficiency Test Data (VIN = 24 V) .............................................................................................................................13

Table 5-3. Efficiency Test Data (VIN = 27 V) .............................................................................................................................13

Table 7-1. UCC14240EVM-052 BOM........................................................................................................................................ 30

Trademarks

All trademarks are the property of their respective owners.

Trademarks www.ti.com

2Using the UCC14240EVM-052 for Biasing Traction Inverter Gate Driver ICs

Requiring Single, Positive or Dual, Positive/Negative Bias Power

SLUUCJ2B – JULY 2021 – REVISED MARCH 2023

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated