SPX50D

SPX50D

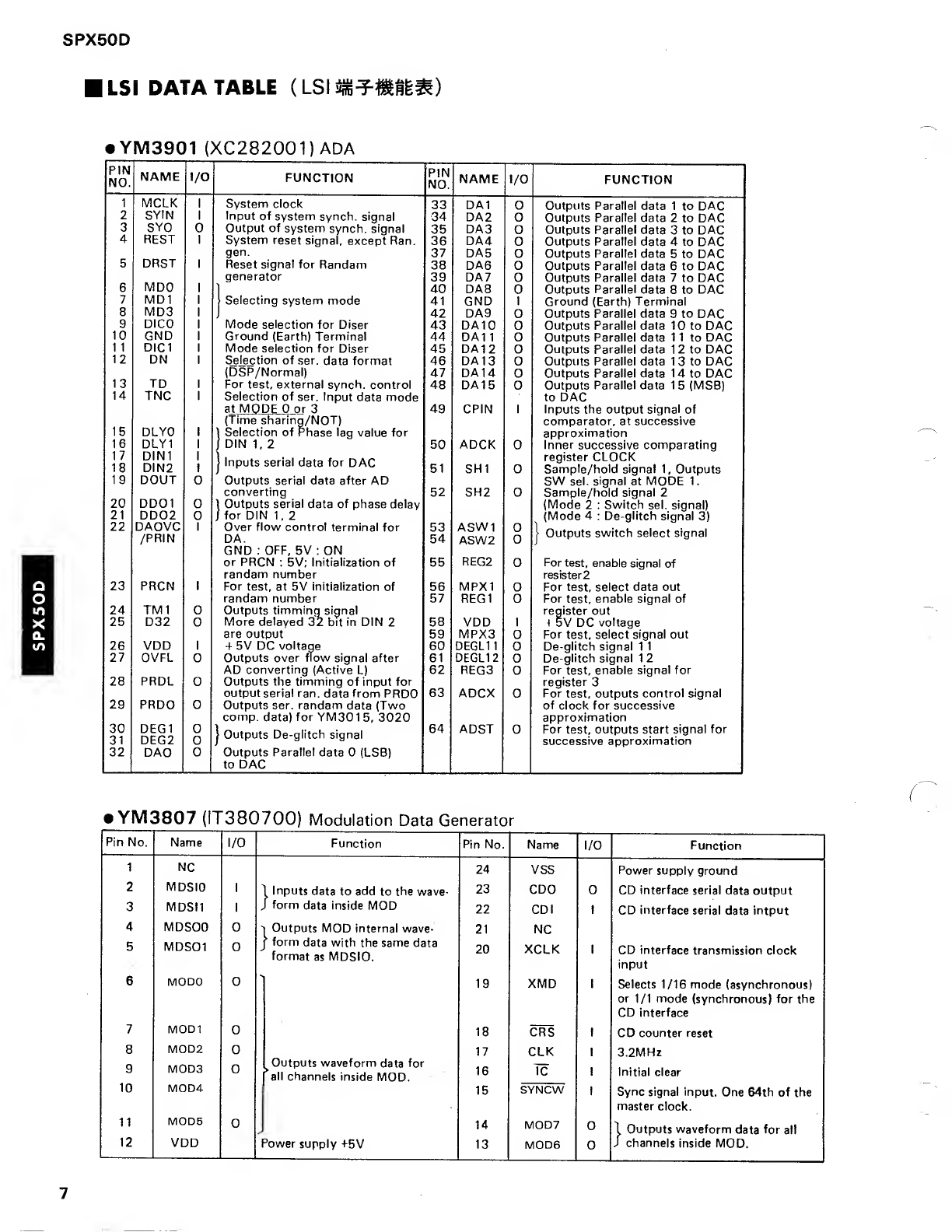

LSI DATA TABLE

•YM3901 (XC28200DADA

FUNCTION PIN

NO. NAME I/O FUNCTION

1MCLK 1System clock 33 DAI 0Outputs Parallel data 1to DAC

2SYIN 1Input of system synch, signal 34 DA2 0Outputs Parallel data 2to DAC

3SYO 0Output of system synch, signal 35 DA3 0Outputs Parallel data 3to DAC

4REST 1System reset signal, except Ran. 36 DA4 0Outputs Parallel data 4to DAC

DRST gen. 37 DA5 0Outputs Parallel data 5to DAC

51Reset signal for Randam 38 DA6 0Outputs Parallel data 6to DAC

MDO generator 39 DA7 0Outputs Parallel data 7to DAC

6140 DA8 0Outputs Parallel data 8to DAC

7MD1 1}Selecting system mode 41 GND 1Ground (Earth) Terminal

8MD3 1)42 DA9 0Outputs Parallel data 9 to DAC

9DICO 1Mode selection for Diser 43 DA10 0Outputs Parallel data 10 to DAC

10 GND 1Ground (Earth) Terminal 44 DAI 10Outputs Parallel data 1 1 to DAC

1 1 DIC1 1Mode selection for Diser 45 DAI 20Outputs Parallel data 12 to DAC

12 DN 1Selection of ser. data format 46 DA13 0Outputs Parallel data 13 to DAC

13 (DSP/Normal) 47 DA14 0Outputs Parallel data 14 to DAC

TD 1For test, external synch, control 48 DA15 0Outputs Parallel data 15 (MSB)

14 TNC 1Selection of ser. Input data mode to DAC

at MODE 0or 349 CPIN 1Inputs the output signal of

(Time sharing/NOT) comparator, at successive

15 DLYO 1\Selection of Phase lag value for approximation

16 DLY1 1/DIN 1,

2

50 ADCK 0Inner successive comparating

17

18 DIN1

DIN2 1

11Inputs serial data for DAC 51 SHI 0register CLOCK

Sample/hold signal 1, Outputs

19 DOUT 0Outputs serial data after AD SW sel. signal at MODE 1

.

20 DD01 converting 52 SH2 0 Sample/hold signal 2

0\Outputs serial data of phase delay (Mode 2:Switch sel. signal)

21 DD02 0/for DIN 1, 2Mode 4:De-glitch signal 3)

22 DAOVC

/PRIN 1Over flow control terminal for

DA. 53

54 ASW1

ASW2 0

01

\Outputs switch select signal

GND :OFF, 5V :ON

or PRCN :5V; Initialization of 55 REG2 0Eor test, enable signal of

randam number resister 2

23 PRCN 1For test, at 5V initialization of 56 MPX1 0For test, select data out

randam number 57 REG1 0For test, enable signal of

24 TM1 0Outputs timming signal

More delayed 32 bit in DIN 2register out

25 D32 058 VDD 1t5V DC voltage

are output 59 MPX3 0For test, select signal out

26 VDD 145V DC voltage 60 DEGL11 0De-glitch signal 11

27 OVFL 0Outputs over flow signal after 61 DEGL12 0De-glitch signal 12

AD converting (Active L) 62 REG3 0For test, enable signal for

28 PRDL 0Outputs the timming of input for register 3

output serial ran. data from PRDO 63 ADCX 0For test, outputs control signal

29 PRDO 0Outputs ser. randam data (Two of clock for successive

30

31 DEG1

DEG2

comp, data) for YM301 5, 3020 approximation

0

01Outputs De-glitch signal 64 ADST 0For test, outputs start signal for

successive approximation

32 DAO 0Outputs Parallel data 0(LSB)

to DAC

•YM3807 (1T380700) Modulation Data Generator

Pin No. Function

^Outputs waveform data for

all channels inside MOD.

Power supply +5V

Pin No.

\Inputs data to add to the wave-

/form data inside MOD

tOutputs MOD internal wave-

Jform data with the same data

format as MDSIO.

Function

Power supply ground

0CD interface serial data output

1CD interface serial data intput

CD interface transmission clock

input

Selects 1/16 mode (asynchronous)

or 1/1 mode (synchronous) for the

CD interface

CD counter reset

3.2MHz

Initial clear

Sync signal input. One 64th of the

master clock.

channels inside MOD.