Analog Devices AD1887 User manual

Other Analog Devices Motherboard manuals

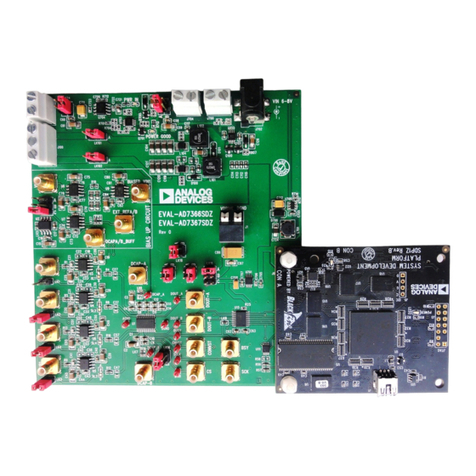

Analog Devices

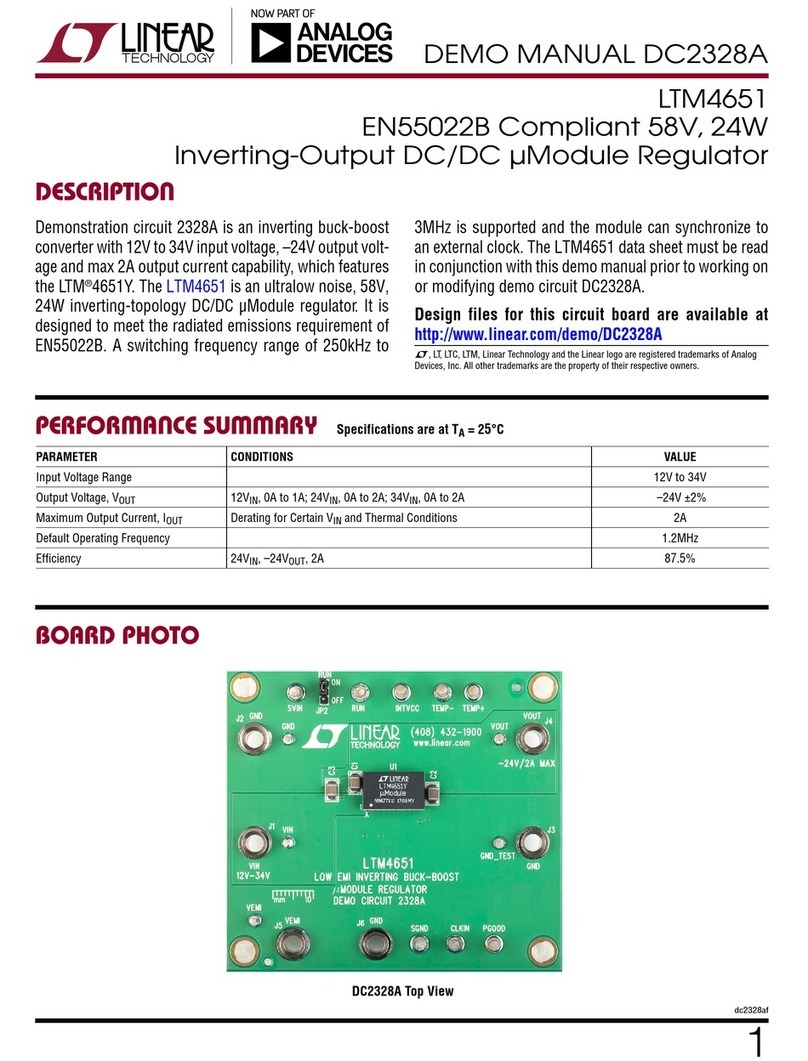

Analog Devices Linear Technology DC2328A Quick setup guide

Analog Devices

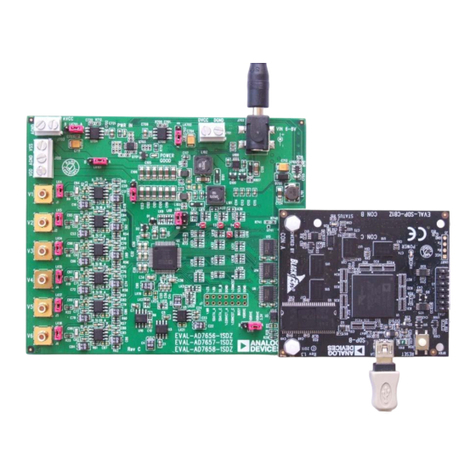

Analog Devices EVAL-AD7656-1SDZ User manual

Analog Devices

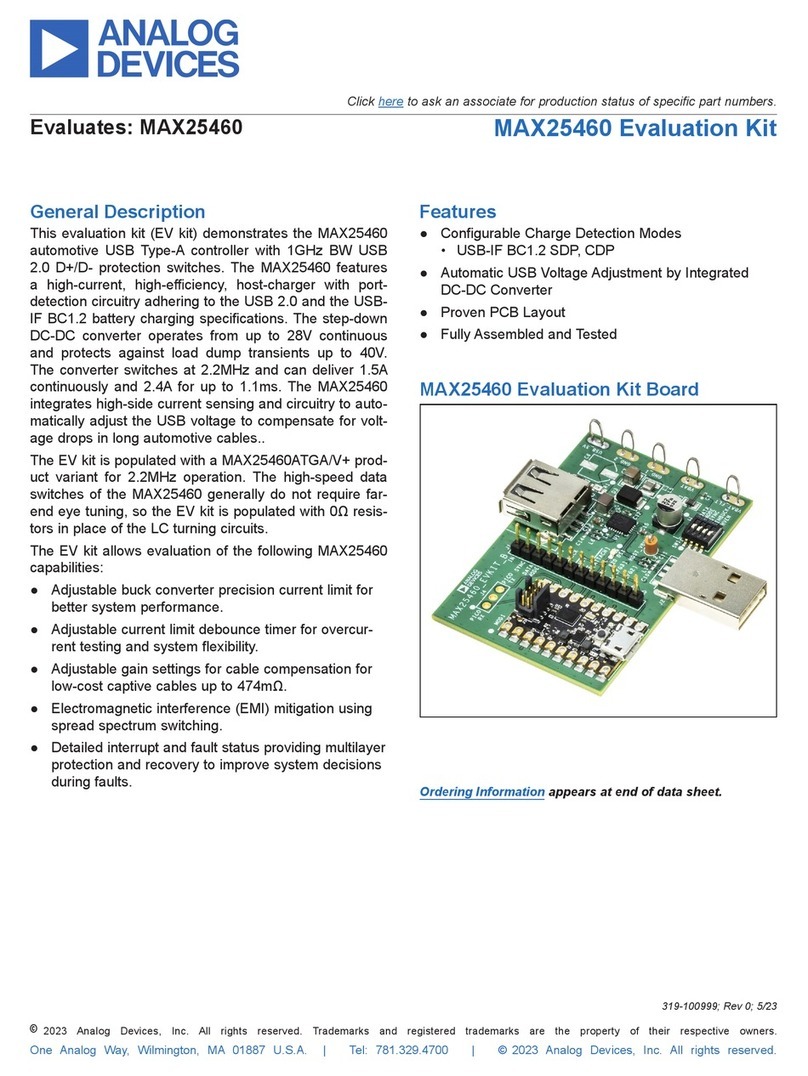

Analog Devices MAX25460 User manual

Analog Devices

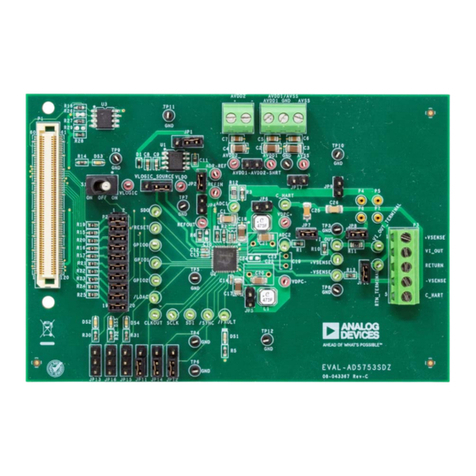

Analog Devices EVAL-AD5753SDZ User manual

Analog Devices

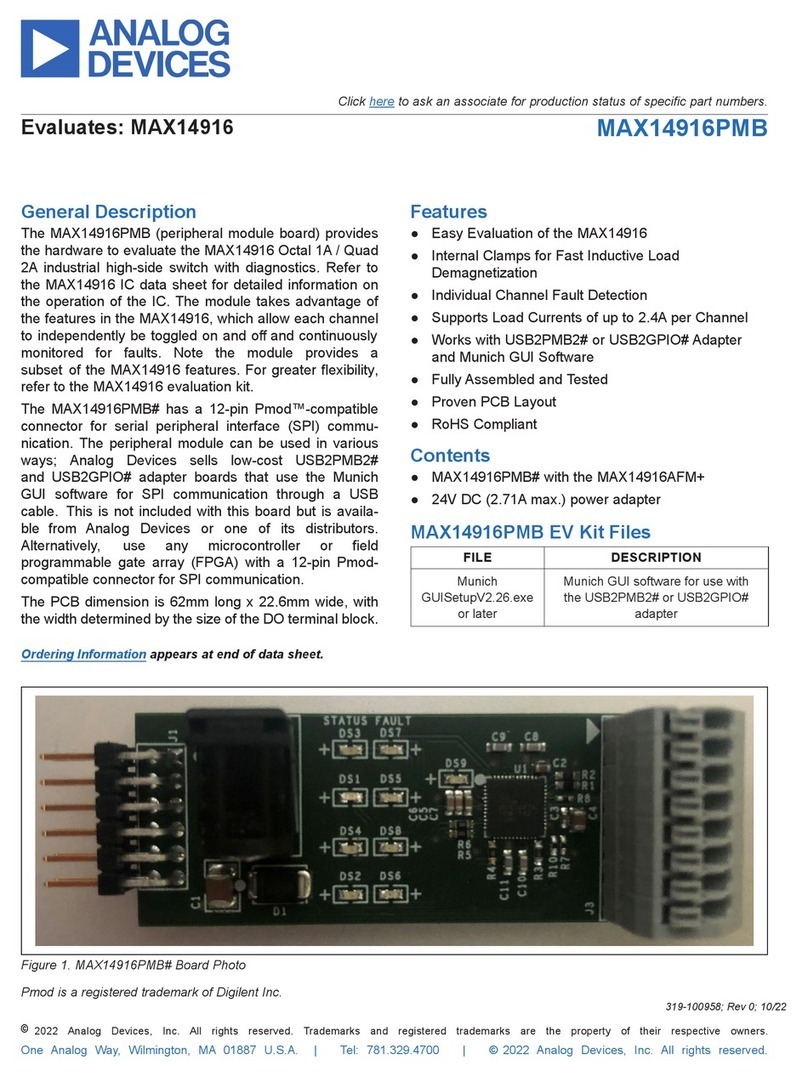

Analog Devices MAX14916PMB User manual

Analog Devices

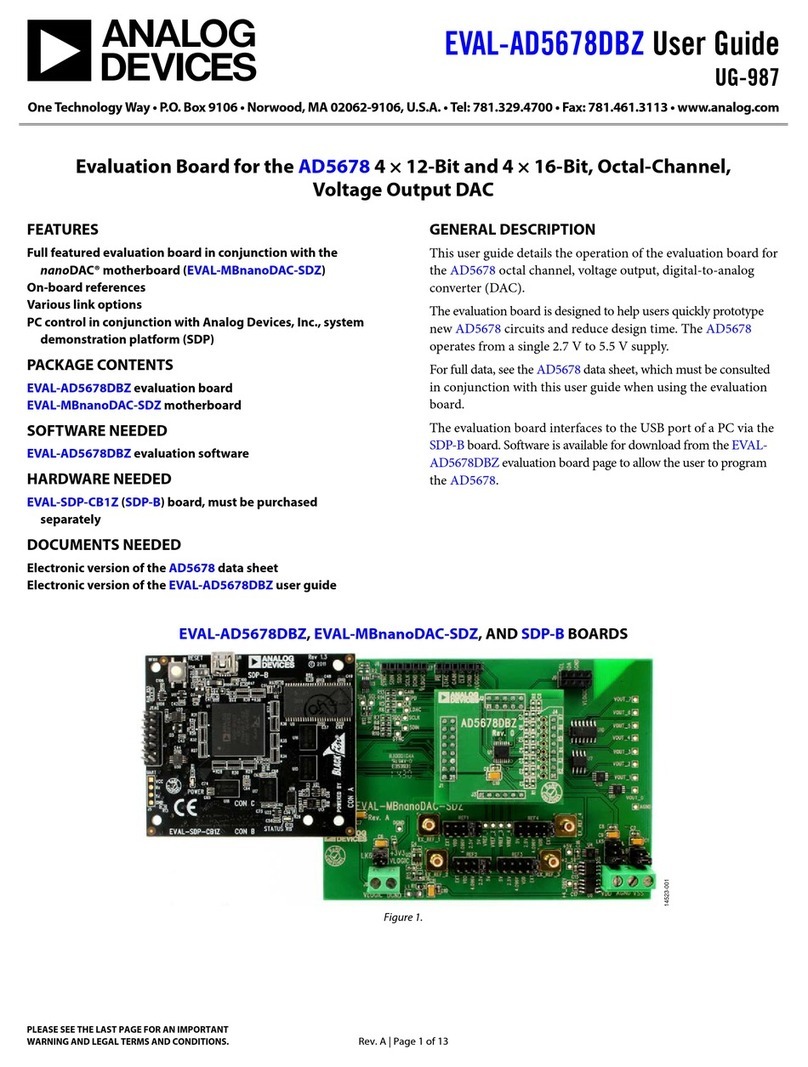

Analog Devices EVAL-AD5678DBZ User manual

Analog Devices

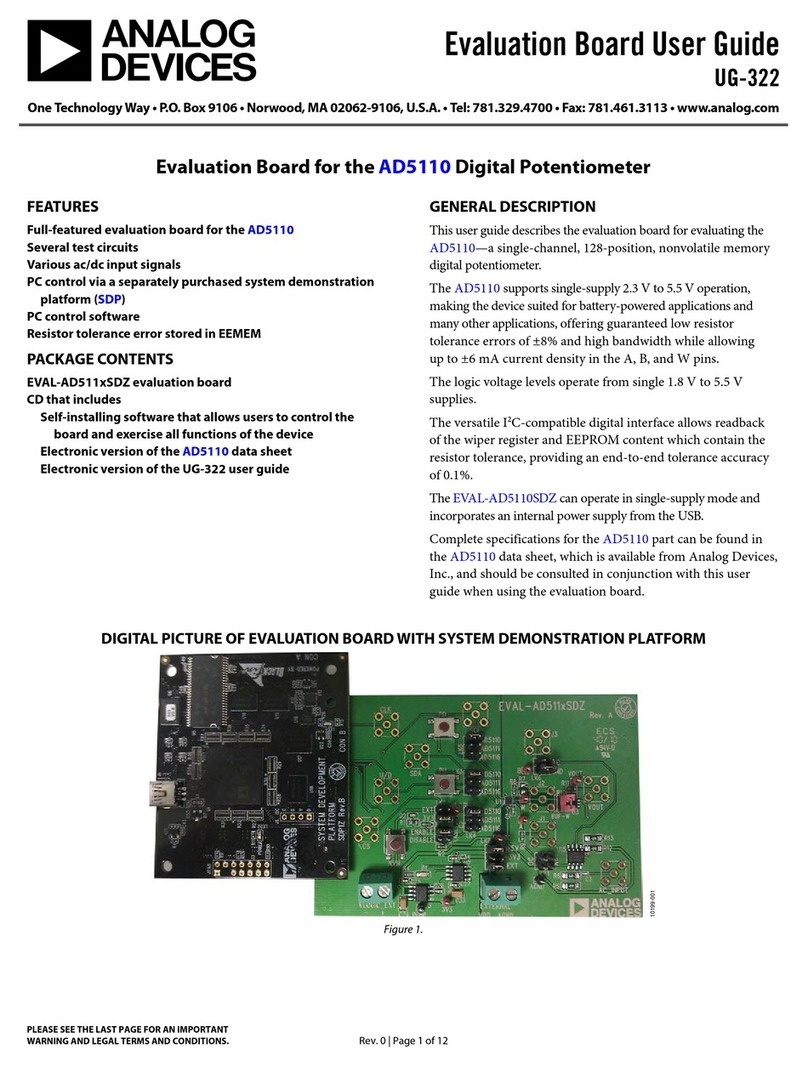

Analog Devices EVAL-AD51150SDZ User manual

Analog Devices

Analog Devices EVAL-AD5341DBZ User manual

Analog Devices

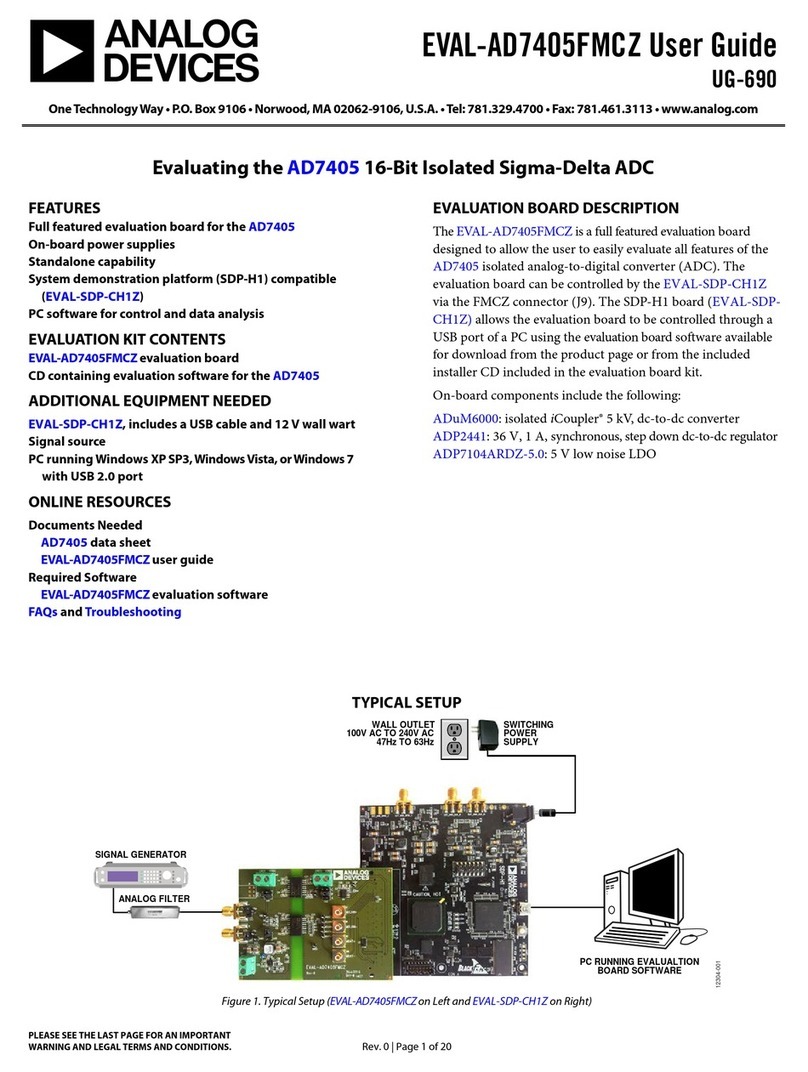

Analog Devices EVAL-AD7405FMCZ User manual

Analog Devices

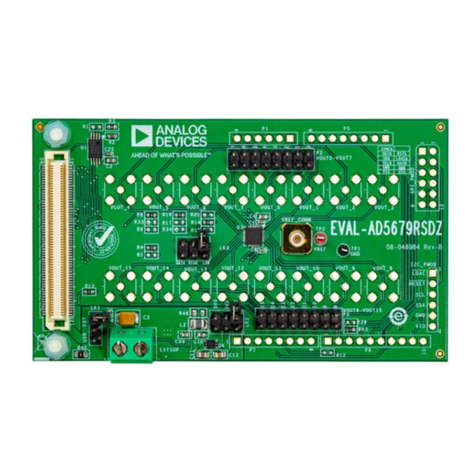

Analog Devices EVAL-AD5679RSDZ User manual

Analog Devices

Analog Devices EVAL-AD4115SDZ User manual

Analog Devices

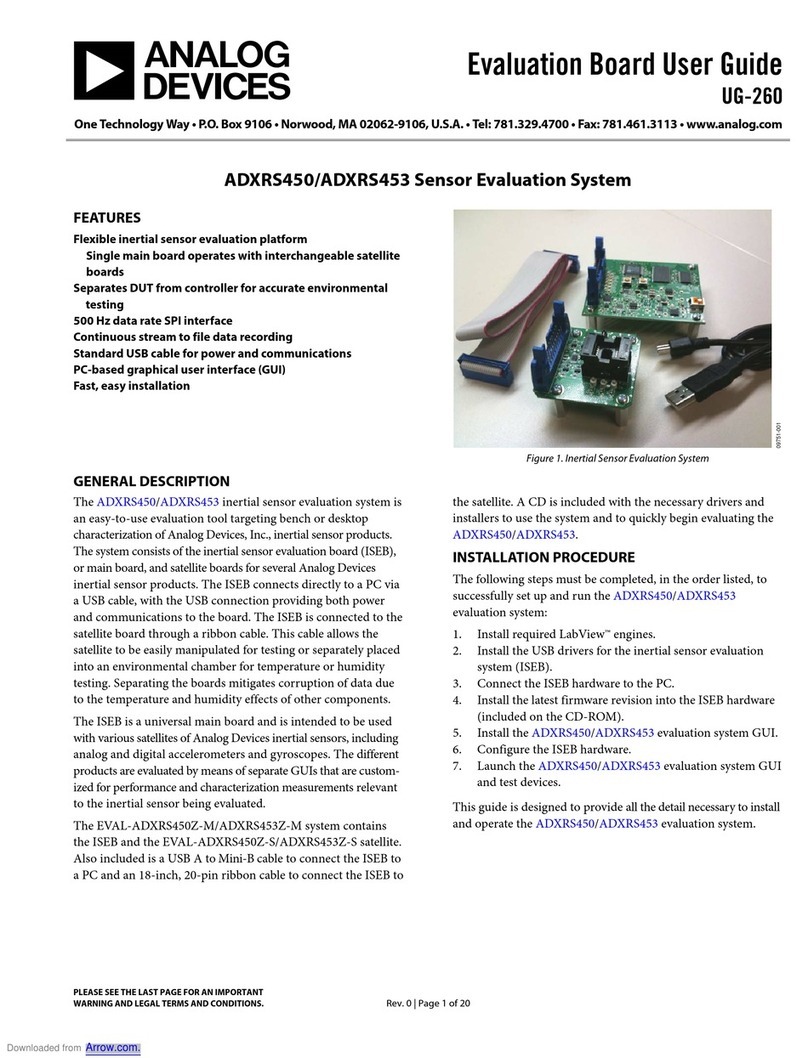

Analog Devices EVAL-ADXRS450Z-M User manual

Analog Devices

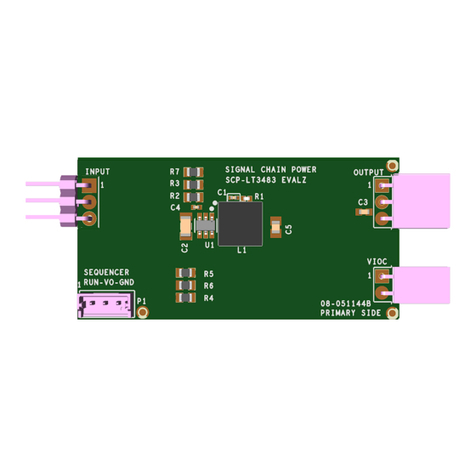

Analog Devices SCP-LT3483-EVALZ Quick setup guide

Analog Devices

Analog Devices ADSP-21160 EZ-KIT Lite User guide

Analog Devices

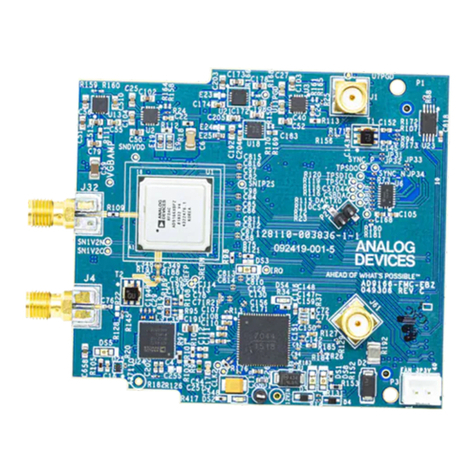

Analog Devices AD9166-FMC-EBZ User manual

Analog Devices

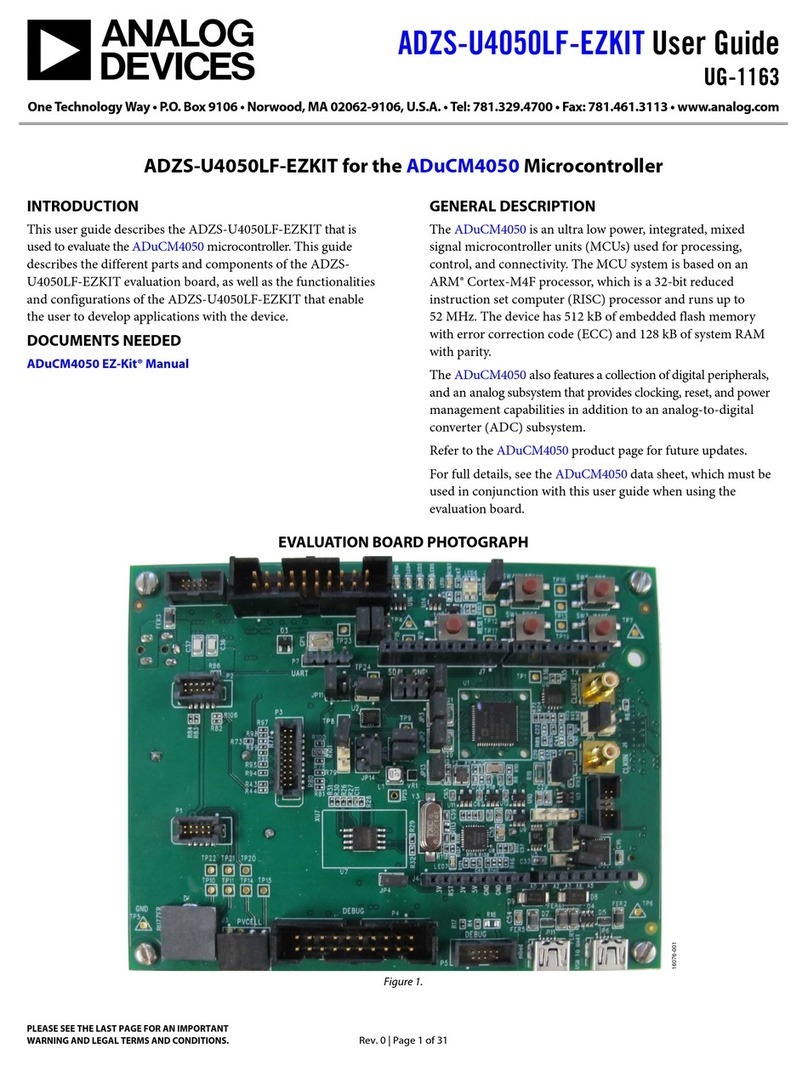

Analog Devices ADZS-U4050LF-EZKIT User manual

Analog Devices

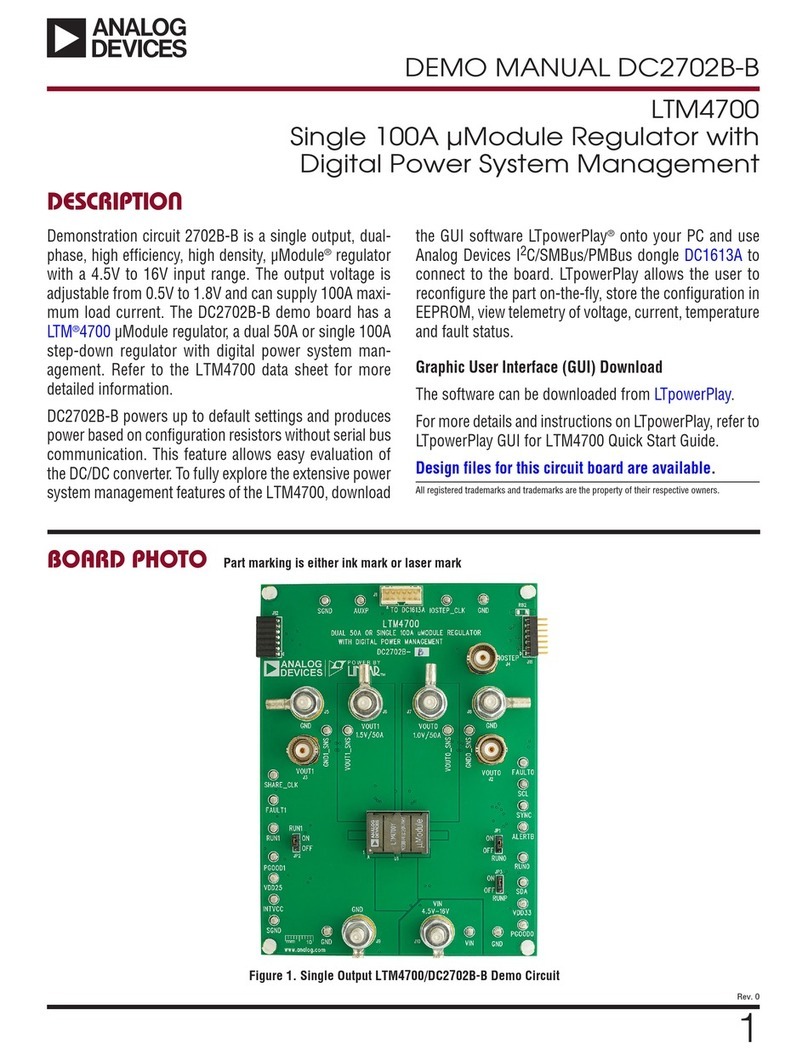

Analog Devices DC2702B-B Quick setup guide

Analog Devices

Analog Devices ADSP-CM403F EZ-KIT Lite User manual

Analog Devices

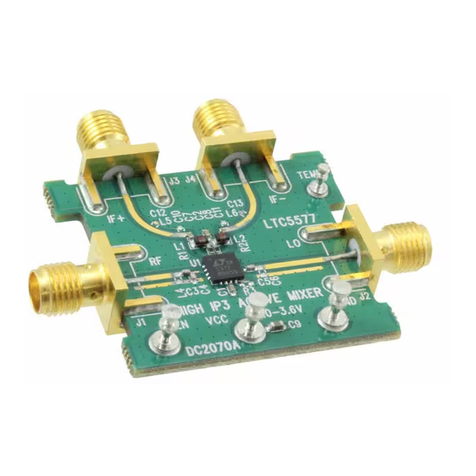

Analog Devices LINEAR TECHNOLOGY LTC5577 User manual

Analog Devices

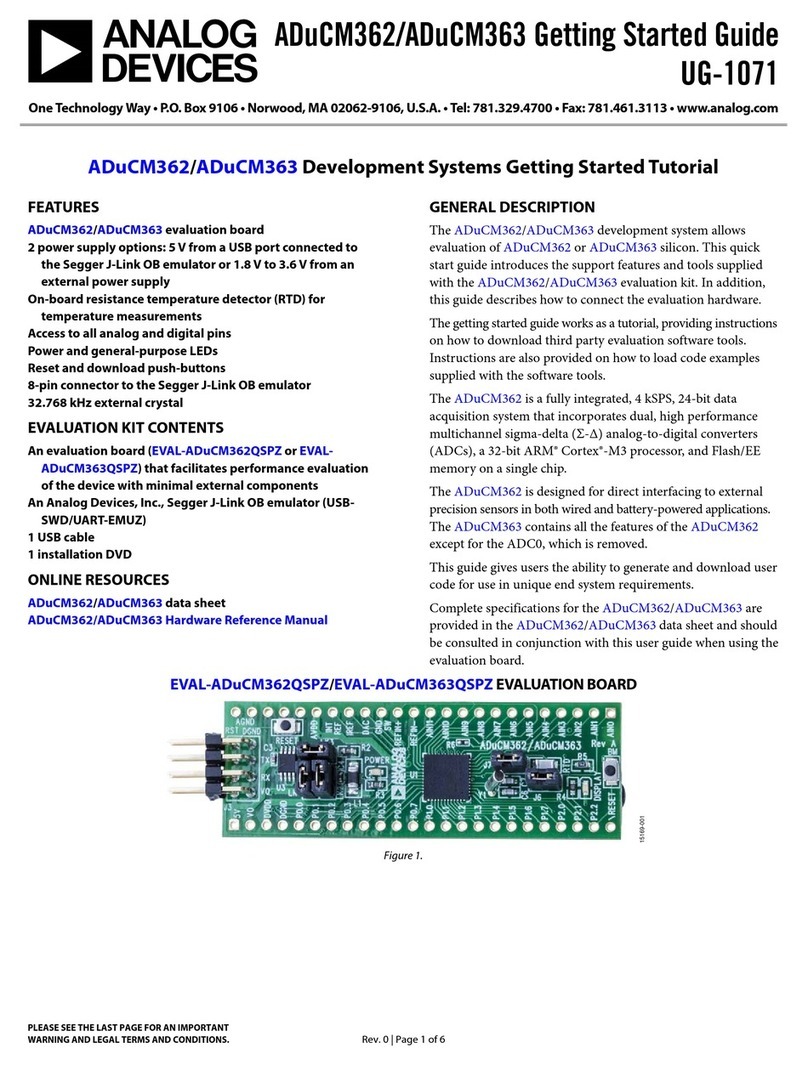

Analog Devices ADuCM362 User manual