AT32F435 & AT32F437 Get Started Guide

2022.4.20 4 Ver 2.0.0

List of Figures

Figure 1. AT32F435 development board.............................................................................................5

Figure 2. Install ArteryTek.AT32F435_437_DFP.................................................................................6

Figure 3. Install Keil4_AT32MCU_AddOn...........................................................................................6

Figure 4. Pack Installer icon in Keil .....................................................................................................7

Figure 5. Keil Debug............................................................................................................................7

Figure 6. Keil Debug Settings..............................................................................................................7

Figure 7. Keil Utilities...........................................................................................................................7

Figure 8. Install IAR_AT32MCU_AddOn.............................................................................................8

Figure 9. IAR Debug............................................................................................................................8

Figure 10. IAR CMSIS-DAP.................................................................................................................8

Figure 11. PLL auto step-by-step system clock switch configuration..................................................9

Figure 12. ICP Programmer –User system data..............................................................................11

Figure 13. User system data - set SRAM size ..................................................................................12

Figure 14. ISP Programmer - Edit User system data........................................................................12

Figure 15. Define Extend_SRAM(void) to change SRAM size.........................................................13

Figure 16. Change SRAM size in Keil startup file .............................................................................14

Figure 17. Change SRAM size in IAR startup file .............................................................................14

Figure 18. ISP programmer –enable access protection...................................................................16

Figure 19. ISP programmer –disable access protection..................................................................16

Figure 20. ICP Programmer –enable erase/program protection......................................................17

Figure 21. ICP programmer –disable erase/program protection......................................................18

Figure 22. Read Cortex model...........................................................................................................18

Figure 23. Read PID and UID............................................................................................................19

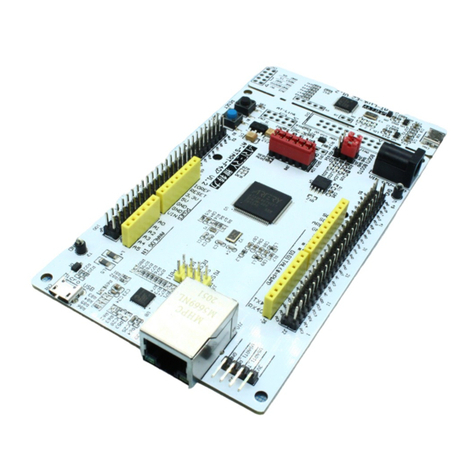

Figure 24.AT-SURF-F437 development board.................................................................................20

Figure 25.Add code to enable FPU ..................................................................................................21

Figure 26. Error: Flash Download failed–“Cortex- 4” ........................................................................21