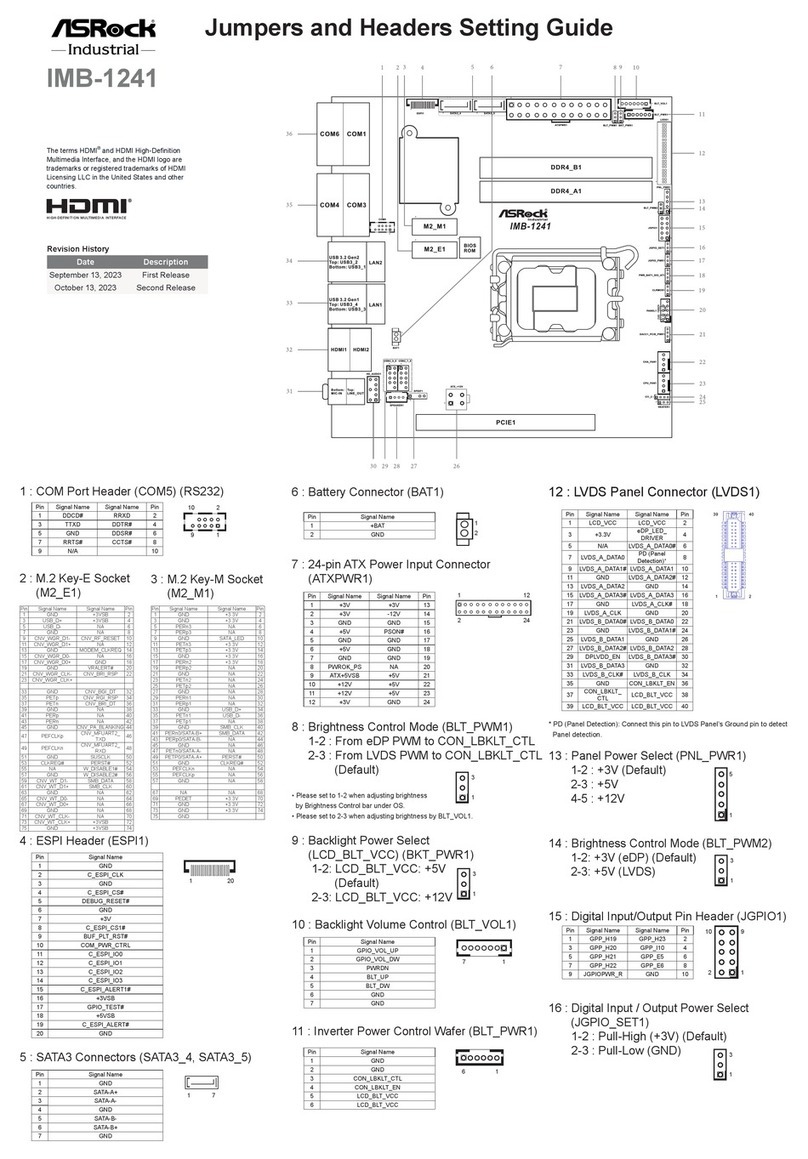

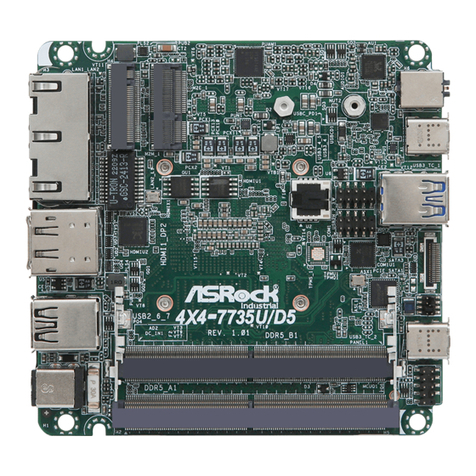

16 : MIOE1

Support interface:

3* PCIe Gen3x1

1* USB3.2 Gen2

1* USB2.0

1* DP1.4

Backside:

17 : DDR5 (DDR5_A1)

18 : C

OM Port Header (COM3)*

19 : C

OM Port Header (COM1)*

6 : M.2 Key-M Socket (M2_M1)

7 : M.2 Key-E Socket (M2_E1)

8 : Battery Connector (BAT1)

9 : 2.5G LAN Port (LAN1)

10 : USB3.2 Gen2 Port (USB3_1)

11 : HDMI Port (HDMI1)

12 : JP_SET1

1-2: AT mode (short), ATX mode (open)

3-5: Auto Clear CMOS (power o)

5-6: Clear CMOS

13 : BIOS ROM (U2)

14 : DC-In Jack (DC_JACK1)

15 : 4-Pin CPU

FAN Connector

1

: USB 2.0 Header (USB2_2_3) (2.0mm Pitch)

2 : Digital Input/Output Pin Header

(JGPIO1)

3 : LVDS_PJ1

4 : BLT_SEL1

5 :

LVDS Panel Connector

Jumpers and Headers Setting Guide

SOM-P104

The terms HDMI™ and HDMI High-Denition

Multimedia Interface, and the HDMI logo are

trademarks or registered trademarks of HDMI

Licensing LLC in the United States and other

countries.

Revision History

Date Description

December 12, 2022 First Release

February 23, 2023 Second Release

March 21, 2023 Third Release

April 27, 2023 Fourth Release

June 27, 2023 Fifth Release

10 9

11

13 12

14

LVDS1

1

1

JGPIO1

M2_E1

1

JP_SET1

BLT_SEL1

LVDS_PJ1

DC_JACK1

U2

HDMI1

USB3.2 Gen2:

USB3_1

1

USB2_2_3

1 1

M2_M1

LAN1

MIOE1

16

CPU_FAN1

1

BAT1

BAT1

1

1

11

SOMP104-

18

19

DDR5_A1 (Support DDR5L Only)

1

COM1

1

COM3

1

HD_AUDIO1

1

PANEL1

Industrial

20

21

MIPI1

1

22

Top Side: Rear Side:

40 2

39 1

Pin Signal Name Signal Name Pin

1 USB_PWR USB_PWR 2

3 P- P- 4

5 P+ P+ 6

7 GND GND 9

9 DUMMY 10

Pin Signal Name Signal Name Pin

1 GND GND 41

2 PCI_RXP1 PCIe_TXP1 42

3 PCI_RXN1 PCIe_TXN1 43

4 GND GND 44

5 PCI_RXP2 PCIe_TXP2 45

6 PCI_RXN2 PCIe_TXN2 46

7 GND GND 47

8 PCI_RXP3 PCIe_TXP3 48

9 PCI_RXN3 PCIe_TXN3 49

10 GND GND 50

11 NC NC 51

12 NC NC 52

13 MIOE_DET# GND 53

14 PCIe_CLKP1 AUDIO_AUX_L 54

15 PCIe_CLKN1 AUDIO_AUX_R 55

16 GND AGND 56

17 SMB_CLK_MAIN HDMI_DDCCLK 57

18 SMB_DATA_MAIN HDMI_DDCDATA 58

19 PCIe_WAKE# ESPI_CLK 59

20 SYS_RESET# ESPI_IO_0 60

21 SLP_S3# ESPI_IO_1 61

22 PWRBTN# ESPI_IO_2 62

23 DDI_HPD# ESPI_IO_3 63

24 GND ESPI_RESET# 64

25 DDI_AUXP ESPI_ALERT# 65

26 DDI_AUXN ESPI_CS0# 66

27 GND GND 67

28 DDI_TXP0 USB3_TXP 68

29 DDI_TXN0 USB3_TXN 69

30 GND GND 70

31 DDI_TXP1 USB3_RXP 71

32 DDI_TXN1 USB3_RXN 72

33 GND GND 73

34 DDI_TXP2 USB2_P+ 74

35 DDI_TXN2 USB2_P- 75

36 GND GND 76

37 DDI_TXP3 +5VSB 77

38 DDI_TXN3 +5VSB 78

39 GND +5VSB 79

40 +12VSB +12VSB 80

1

40

41

80

Pin Signal Name Signal Name Pin

1 LCD_VCC LCD_VCC 2

3 +3.3V N/A 4

5 N/A LVDS_A_DATA0# 6

7 LVDS_A_DATA0 GND 8

9 LVDS_A_DATA1# LVDS_A_DATA1 10

11 GND LVDS_A_DATA2# 12

13 LVDS_A_DATA2 GND 14

15 LVDS_A_DATA3# LVDS_A_DATA3 16

17 GND LVDS_A_CLK# 18

19 LVDS_A_CLK GND 20

21 LVDS_B_DATA0# LVDS_B_DATA0 22

23 GND LVDS_B_DATA1# 24

25 LVDS_B_DATA1 GND 26

27 LVDS_B_DATA2# LVDS_B_DATA2 28

29 DPLVDD_EN LVDS_B_DATA3# 30

31 LVDS_B_DATA3 GND 32

33 LVDS_B_CLK# LVDS_B_CLK 34

35 GND CON_LBKLT_EN 36

37 CON_LBKLT_CTL LCD_BLT_VCC 38

39 LCD_BLT_VCC LCD_BLT_VCC 40

2 10

1 9

1

2

9

10

1

2

9

10

1

2

9

10

Pin Signal Name Signal Name Pin

1 SIO_GP63 GPP_B15 2

3 SIO_GP64 GPP_E1 4

5 SIO_GP86 GPP_E2 6

7 SIO_GP87 GPP_E13 8

9 +JGPIOPWR GND 10

Pin Signal Name Signal Name Pin

1 +3V PLVDD 2

3 +5V PLVDD 4

5 +5V BLTVCC 6

7 +12V BLTVCC 8

9 +12V BLTVCC 10

Pin Signal Name Signal Name Pin

1 BLT_VCC BLDN 2

3 BLT_VCC BLUP 4

5 BLT_EN PWRDN 6

7 BLT_CTL GPIO_TEST# 8

9 GND GND 10

Pin Signal Name

1 +BAT

2 GND

1 2

1

2

9

10

Pin Signal Name Signal Name Pin

1 AT/ATX mode GND 2

3 RTCRST2# GND 4

5 RTC RST# GND 6

7 JGPIO_VSET GND 8

9 JGPIO_VSET +3V 10

Pin Signal Name

1 GND

2 +5V

3 FAN_SPEED

4 FAN_SPEED_CONTROL

1

4

12

9

10

Pin Signal Name Signal Name Pin

1 DDCD#3 RRXD3 2

3 TTXD3 DDTR#3 4

5 GND DDSR#3 6

7 RRTS#3 CCTS#3 8

9 N/A N/A 10

Pin Signal Name Signal Name Pin

1 DDCD#1 RRXD1 2

3 TTXD1 DDTR#1 4

5 GND DDSR#1 6

7 RRTS#1 CCTS#1 8

9 N/A N/A 10

12

9

10

Pin Signal Name Signal Name Pin

1 GND +3.3V 2

3GND +3.3V 4

5NA NA 6

7NA NA 8

9GND HD_LED 10

11 NA +3.3V 12

13 NA +3.3V 14

15 GND +3.3V 16

17 NA +3.3V 18

19 NA NA 20

21 GND NA 22

23 NA NA 24

25 NA NA 26

27 GND NA 28

29 NA NA 30

31 NA NA 32

33 GND USB D+ 34

35 NA USB D- 36

37 NA NA 38

39 GND SMB_CLK 40

41 PERn0/SATA-B+ S M B _ DATA 42

43 PERp0/SATA-B- NA 44

45 GND NA 46

47 PETn0/SATA-A- NA 48

49 PETP0/SATA-A+ PERST# 50

51 GND CLKREQ# 52

53 PEFCLKn WAKE# 54

55 PEFCLKp NA 56

57 GND NA 58

67 NA NA 68

69 PEDET +3.3V 70

71 GND +3.3V 72

73 GND +3.3V 74

75 GND

Pin Signal Name Signal Name Pin

1 GND +3VSB 2

3USB_D+ +3VSB 4

5USB_D- NA 6

7GND NA 8

9CNV_WGR _ D1- CNV_RF_RESET 10

11 CNV_WGR_D1+ NA 12

13 GND MODEM_CLKREQ 14

15 CNV_WGR _ D0- NA 16

17 CNV_WGR _ D0+ GND 18

19 GND BC_PROCHOT 20

21 CNV_WGR _CLK- CNV_BRI_RSP 22

23 CNV_WGR _CLK+

CNV_BGI_DT 32

33 GND CNV_RGI_RSP 34

35 PETp CNV_BRI_DT 36

37 PETn NA 38

39 GND NA 40

41 PERp NA 42

43 PERn CNV_PA_BLANKING 44

45 GND CNV_MFUART2_TXD 46

47 PEFCLKp CNV_MFUART2_RXD 48

49 PEFCLKn SUSCLK 50

51 GND PERST# 52

53 CLKREQ# W_DISABLE1# 54

55 NA W_DISABLE2# 56

57 GND SMB_DATA 58

59 CN V_WT_D1- SMB_CLK 60

61 CN V_WT_D1+ NA 62

63 GND NA 64

65 CN V_WT_D0- NA 66

67 CN V_WT_D0+ NA 68

69 GND NA 70

71 CN V_WT_CLK- +3VSB 72

73 CNV_W T_CLK+ +3VSB 74

75 GND

* This motherboard supports RS232/422/485 on COM1 and COM3

ports. Please refer to the table below for the pin denition. In adition,

COM1 and COM3 ports (RS232/422/485) can be adjusted in BIOS

setup utility > Advanced Screen > Super IO Conguration. You may

refer our manual for details.

COM1, COM3 Ports Pin Denition

Pin RS232 RS422 RS485

1 DCD# TX- DATA-

2 RXD TX+ DATA+

3 TXD RX+ N/A

4 DTR# RX- N/A

5 GND GND GND

6 DSR# N/A N/A

7 RTS# N/A N/A

8 CTS# N/A N/A

9 N/A N/A N/A