2

Specification........................................................................................................................5

General Specifications...............................................................................................................5

Receiver Specifications .............................................................................................................6

Transmitter Specifications .........................................................................................................7

Barrett 2040, Barrett 2050 compliance..............................................................................8

FCC RF exposure compliance statement..................................................................................8

FCC RF exposure warning ........................................................................................................9

FCC modulation modes .............................................................................................................9

Industry Canada modulation modes ..........................................................................................9

Introduction.......................................................................................................................11

The use of DSP in the receiver ...........................................................................11

The use of DSP in the transmitter .......................................................................11

Other refinements................................................................................................11

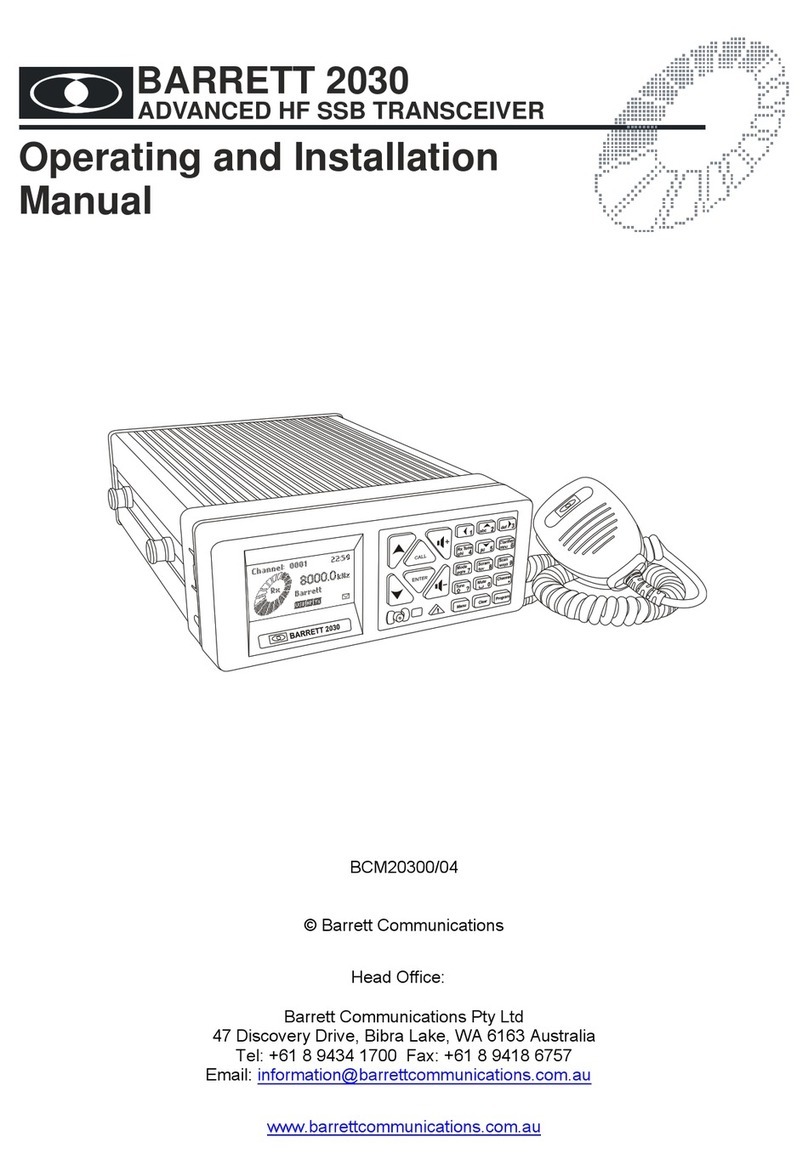

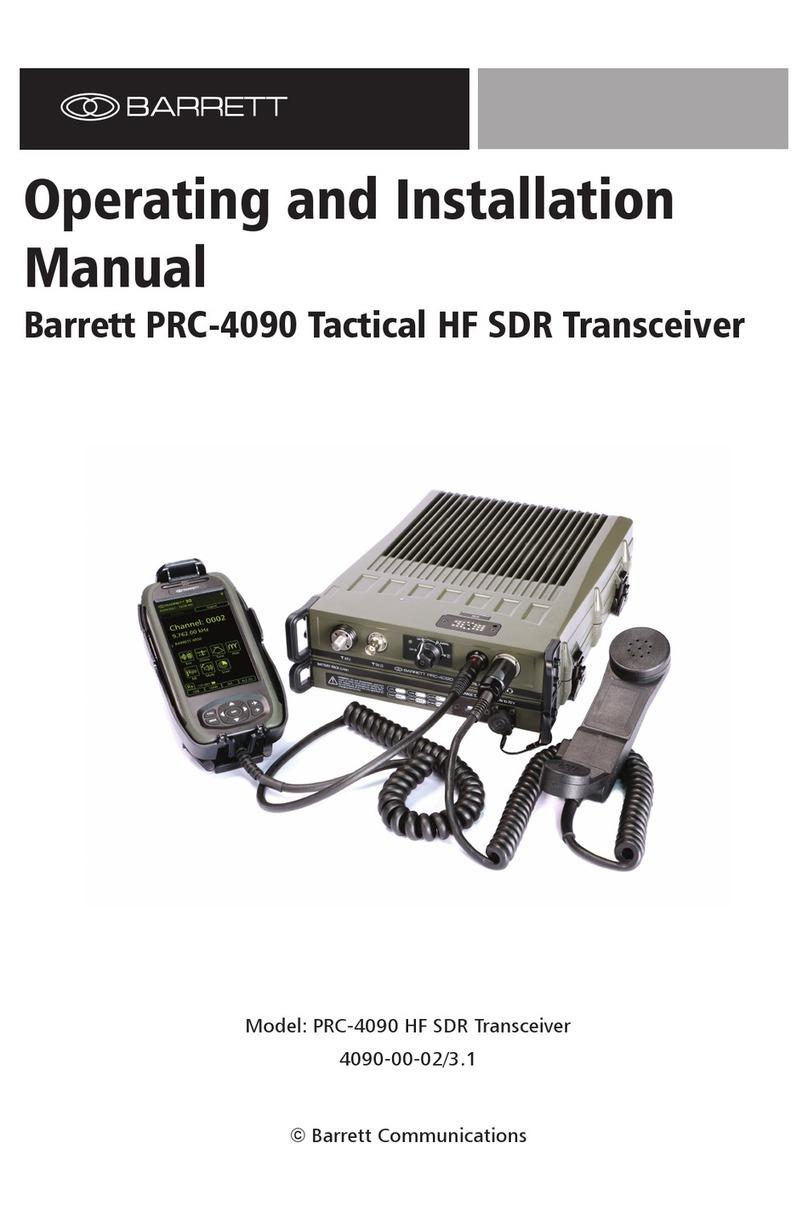

Overview............................................................................................................................12

Control Head............................................................................................................................12

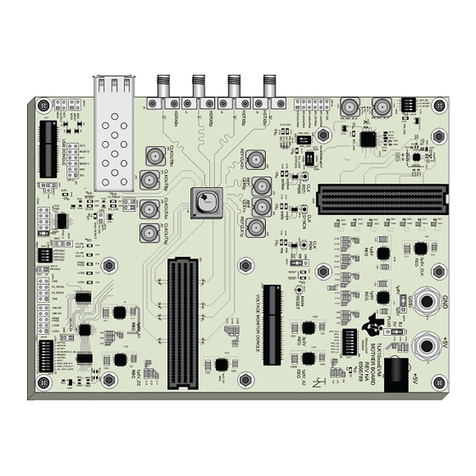

Microprocessor/ RF Audio PCB...............................................................................................12

Microprocessor section .......................................................................................12

RF section ...........................................................................................................12

Power amplifier PCB................................................................................................................13

Technical description.......................................................................................................14

Microprocessor / RF PCB – microprocessor section...............................................................14

Reference oscillator 22.7275 kHz .......................................................................14

Microprocessor....................................................................................................14

DDFS and VCO...................................................................................................14

VCO.....................................................................................................................14

Phase detector ....................................................................................................14

VCO divider ratio .................................................................................................15

Selcall (if enabled)...............................................................................................15

Audio mute ..........................................................................................................15

Audio Filtering .....................................................................................................15

Noise reduction ...................................................................................................15

Microprocessor / RF PCB – RF section...................................................................................15

First mixer............................................................................................................16

Post mixer amplifier Q5.......................................................................................16

First IF filter F1, F2 ..............................................................................................16

Second mixer U48...............................................................................................16

455 kHz IF amplifier ............................................................................................17

AGC.....................................................................................................................17

Carrier insertion generator ..................................................................................17

Third mixer (Product detector) ............................................................................17

Speaker output ....................................................................................................17

Tones ..................................................................................................................18

Transmit ...................................................................................................................................18

Microphone input. Remote head / Front Panel ...................................................18

Line input.............................................................................................................18

Microphone / Line input selection........................................................................18

Compression .......................................................................................................18

Transmit tones.....................................................................................................19

Post DSP (Transmit direction).............................................................................19

455 kHz IF processing.........................................................................................19

Second mixer ......................................................................................................19

First mixer............................................................................................................19

Noise blanker ......................................................................................................19

Power amplifier (PA) PCB .......................................................................................................20

Gain control amp .................................................................................................20