Safety Precautions

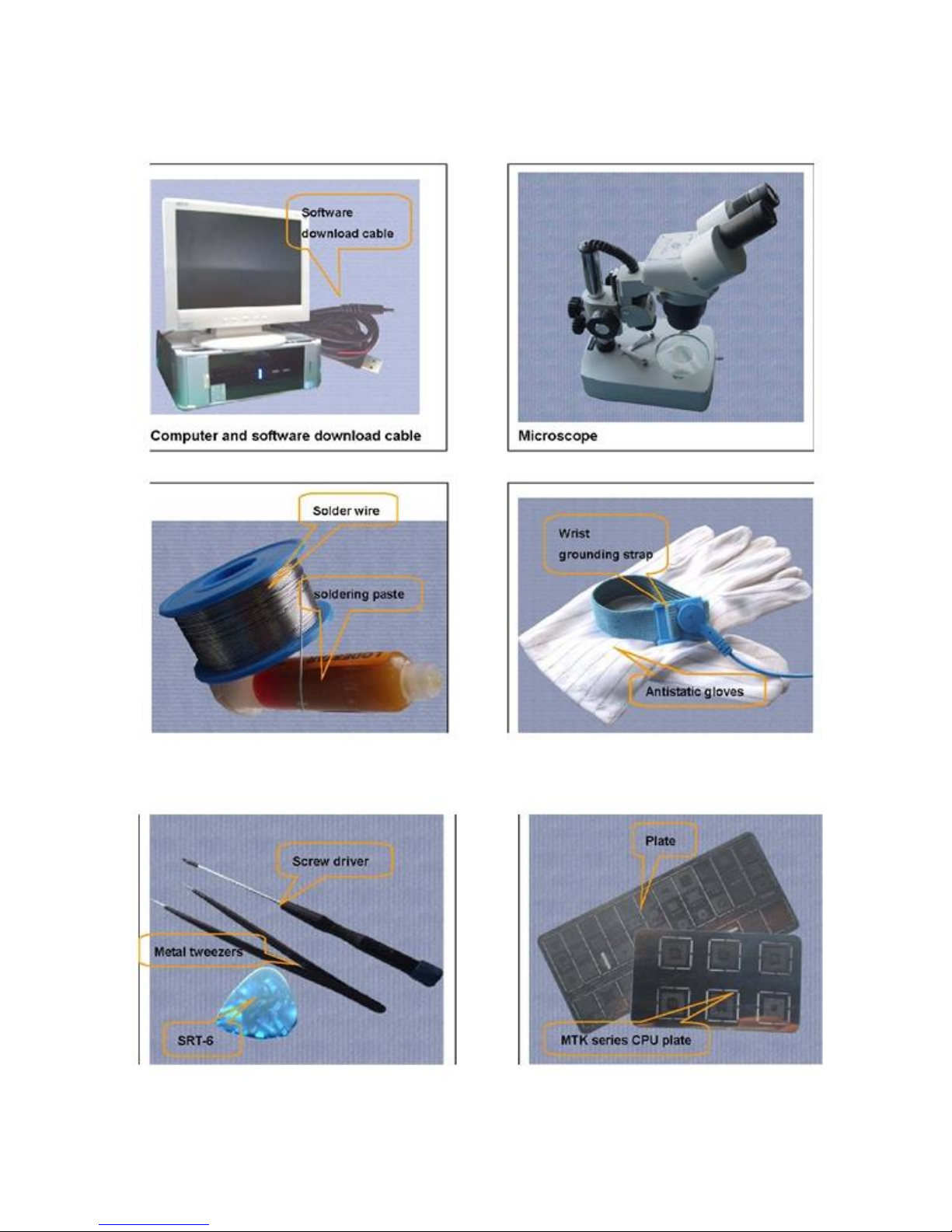

Repair Precaution

Repair in Shield Box, during detailed tuning .Take specially care of tuning or test,

because specificity of cellular phone is sensitive for surrounding interference(RF noise).

Be careful to use a kind of magnetic object or tool, because performance of parts is

damaged by the influence of magnetic force.

Surely use a standard screwdriver when you disassemble this product, otherwise

screw will be worn away.

Use a thicken twisted wire when you measure level. A thicken twisted wire has low

resistance, therefore error of measurement is few.

Repair after separate Test Pack and Set because for short danger (for example an

overcurrent and furious flames of parts etc) when you repair board in condition of connecting Test

Pack and tuning on.

Take specially care of soldering, because Land of PCB is small and weak in heat.

Surely tune on/off while using AC power plug, because a repair of battery charger is

dangerous when tuning ON/OFF PBA and Connector after disassembling charger.

Don't use as you pleases after change other material than replacement registered on

SEC System. Otherwise engineer in charge isn't charged with problem that you don't keep

this rules.

ESD(Electrostatically Sensitive Devices) Precaution

Several semiconductors may be damaged easily by static electricity.

Such parts are called by ESD(Electrostatically Sensitive Devices),

for example IC,BGA chip etc. Read precaution below. You can prevent from ESD

damage by static electricity.

Remove static electricityremained your bodybefore you touch semiconductor or parts

with semiconductor. There are ways that you touch an earthed place or wear static electricity

prevention string on wrist.

Use earthed soldering steel when you connect or disconnect ESD.

Use soldering removing tool to break static electricity. Otherwise ESD will be

damaged by static electricity.

Don't unpack until you set up ESD on product. Because most of ESD are packed by box

and aluminum plate to have conductive power, they are prevented from static electricity.

You must maintain electric contact between ESD and place due to be set up until ESD

is connected completely to the proper place or a circuit board.