Titanium Interfaces User Guide

Contents

About the Interface Designer.........................................................................................................iv

Chapter1:Get Oriented.................................................................................................................. 5

Interface Blocks..........................................................................................................................................7

Package/Interface Support Matrix...........................................................................................................8

Interface Block Connectivity.................................................................................................................... 8

Designing an Interface............................................................................................................................. 9

Create or Delete a Block....................................................................................................................... 10

Using the Resource Assigner................................................................................................................ 11

Resource View..............................................................................................................................12

Importing and Exporting Assignments.....................................................................................13

Interface Designer Output Files............................................................................................................15

Scripting an Interface Design................................................................................................................15

Chapter2:Device Settings............................................................................................................17

Configuration Interface...........................................................................................................................17

Enable Internal Configuration....................................................................................................17

About SEU Detection.................................................................................................................. 17

Enable SEU Detection.................................................................................................................18

SEU Detection Circuitry.............................................................................................................. 19

Design Check: Configuration Messages............................................................................................. 20

I/O Banks Interface................................................................................................................................. 21

Titanium I/O Banks................................................................................................................................. 21

Dynamic Voltage Support......................................................................................................................22

Design Check: I/O Bank Messages......................................................................................................23

Chapter3:Clock and Control Networks....................................................................................... 24

Clock Sources that Drive the Global and Regional Networks.......................................................... 26

Configuring the Dynamic Clock Multiplexers..................................................................................... 27

Driving both the Global and Regional Networks............................................................................... 27

Design Check: Clock Control Messages............................................................................................. 28

Chapter4:DDR Interface.............................................................................................................. 31

About the DDR DRAM Interface............................................................................................................ 31

DDR Interface Designer Settings.......................................................................................................... 37

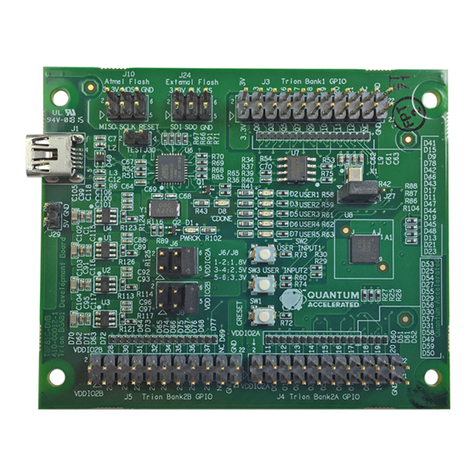

Chapter5:GPIO Interface............................................................................................................. 39

Types of GPIO...........................................................................................................................................39

Features for HVIO and HSIO Configured as GPIO.............................................................................41

Double-Data I/O.......................................................................................................................... 42

Programmable Delay Chains..................................................................................................... 43

About the HVIO Interface....................................................................................................................... 44

About the HSIO Interface....................................................................................................................... 46

HSIO Configured as GPIO.....................................................................................................................47

Using the GPIO Block.............................................................................................................................50

Using the GPIO Bus Block..................................................................................................................... 53

Create a TX Serializer Interface............................................................................................................ 54

Create a RX Deserializer Interface........................................................................................................55

Design Check: GPIO Messages............................................................................................................ 56

Chapter6:LVDS Interface............................................................................................................. 67

HSIO Configured as LVDS..................................................................................................................... 67

Using the LVDS Block.............................................................................................................................73

Create an LVDS TX Interface................................................................................................................. 75

www.efinixinc.com