GS61004B-EVBCD

GaN E-HEMT Full Bridge Evaluation Board

User’s Guide

_____________________________________________________________________________________________________________________

GS61004B-EVBCD Rev 200106 © 2020 GaN Systems Inc. www.gansystems.com 8

Please refer to the Evaluation Board/Kit Important Notice on page 27

Circuit Description

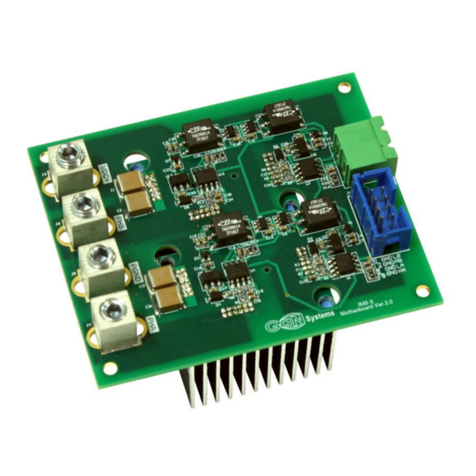

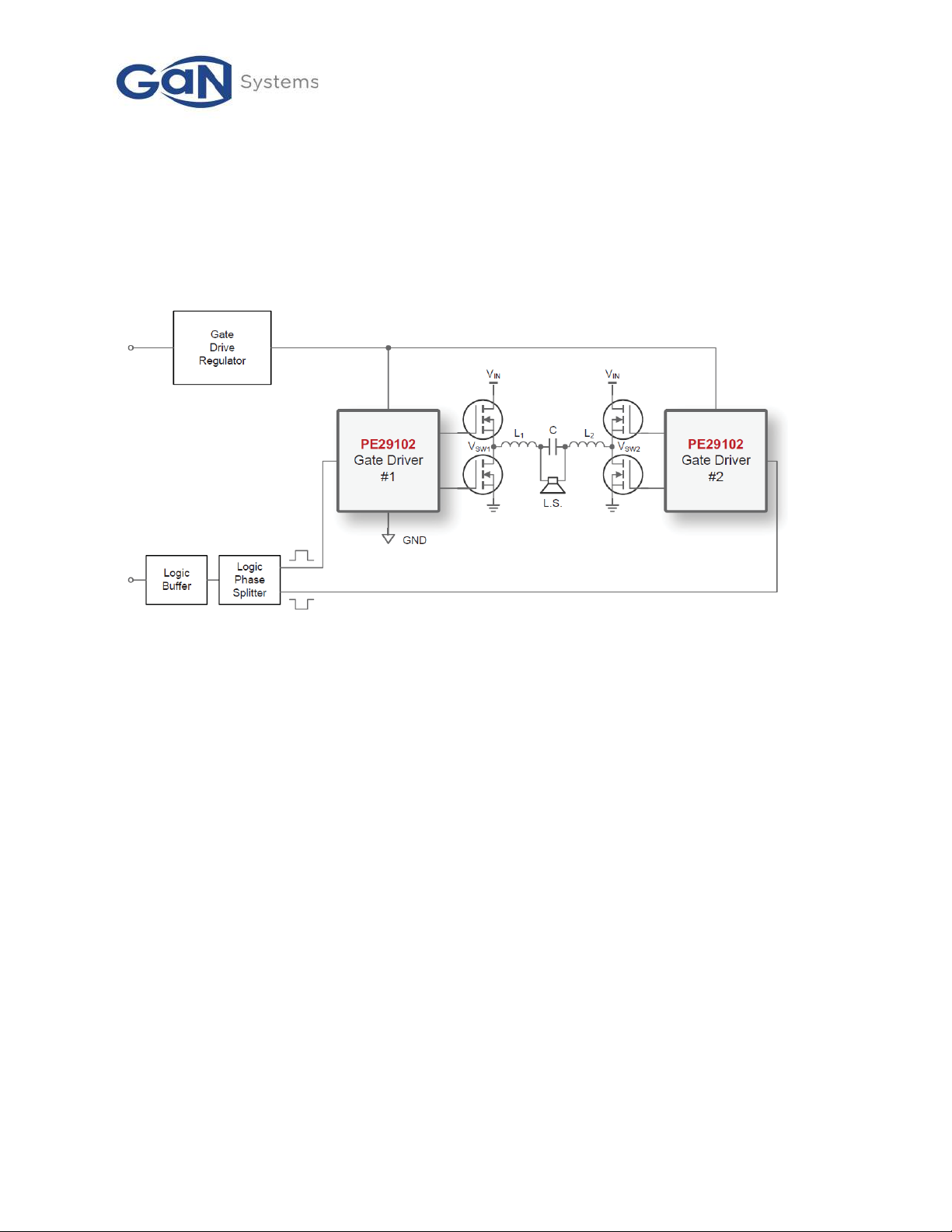

The full-bridge circuit comprises two half bridges which share a common supply and load.

The high voltage (+12 to 30V DC max) to the high-side GS61004B E-HEMTs are fed via J7 and then

through the overcurrent protection circuit around Q7, which is described separately. The low-level

logic circuitry is supplied by a 6 Volt regulator U7, which is fed separately through P1 with +8 to

+24V DC (nominal +12V DC). This feeds the optimal 6V to both of the PE29102 drivers U6 and U8,

which are driven independently by a common logic X-OR gate Phase Splitter (Inverter)

configuration U5, which is in turn driven by a single input buffer, U9. The latter two devices are

also capable of 6V operation.

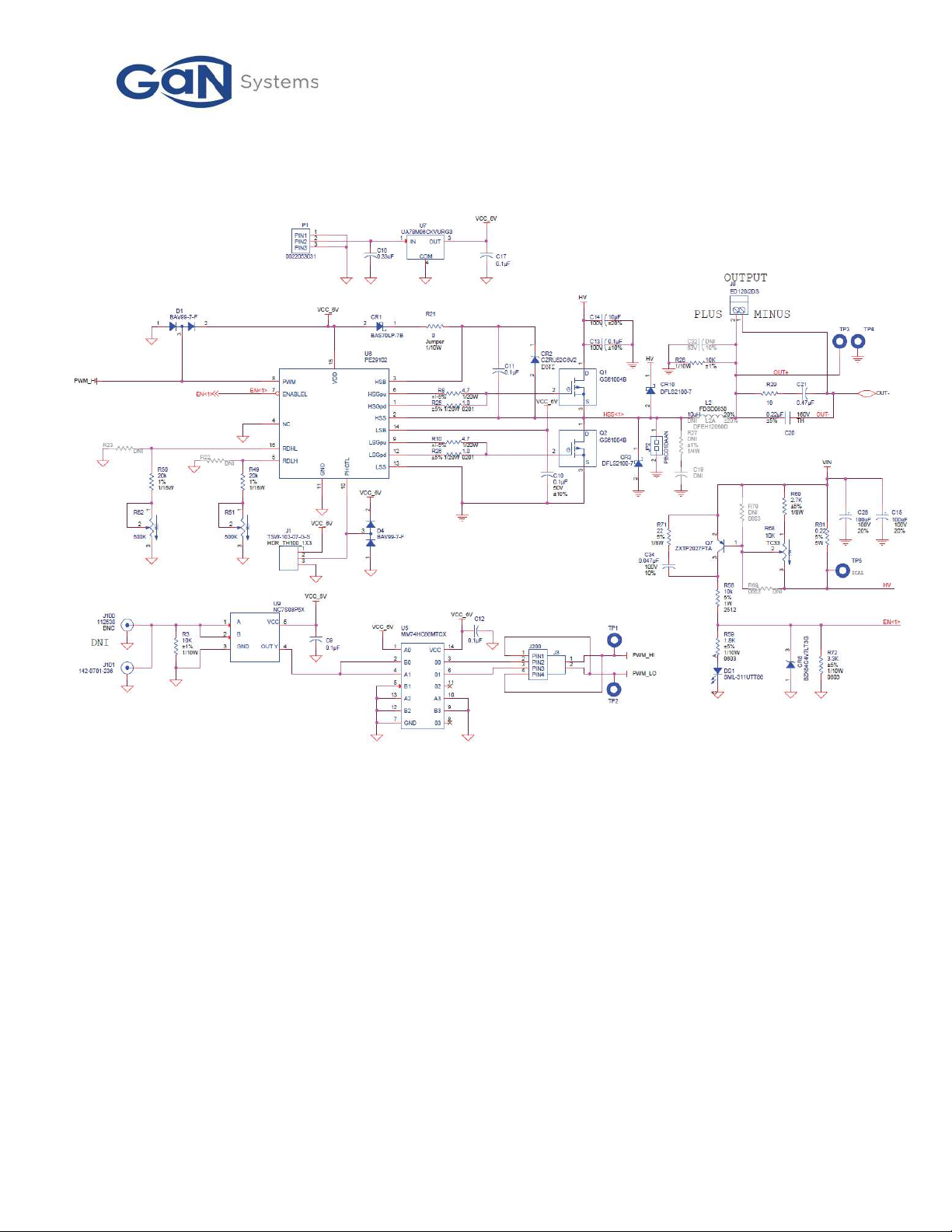

Typically, the PWM signal is brought in at J100/101 (usually a 50 Ohm BNC socket, though SMA

and SMB options are possible) on 50 Ohm coax (for example, RG174) and terminated with R3,

whose value is chosen to present a light, rather than matched, load into U9.

Jumpers J200 and J3 are provided to allow for experimental choices of phasing of the two half-

bridges, the default setting being that each half bridge driver IC is fed with opposing phases. Each

PE29102 has a pin (10) that allows for local phase reversal by fitting and changing one or both

jumpers J1 or J2. Both options have been included on the board to allow for maximum flexibility as

well as some empirical lab-testing to evaluate the relative merits of either approach in practice.

Test Points TP1 and TP2 allow for convenient oscilloscope monitoring of the jumper-configured drive

waveforms derived from the PWM input.

The propagation delays between the PWM input at J100/101 and the output switching nodes at JP2

and JP3 are of the order of 45 ns. This reduces to approximately 10 ns if the TTL/XOR circuitry is

bypassed and disconnected by taking the PWM input signal directly to TP1 and TP2 and

disconnecting any jumpers fitted to J200.Then the required phase inversion for complementary full

bridge operation can be performed by switching over either of the PHCTL jumper links J1 or J2,

but not both. This also improves relative timing and symmetry compared to the "stock" TTL/XOR

phase inversion, should this be required in critical or higher frequency applications.

Trimpots R51 and R52 adjust the dead time for driver U6, and similarly R53 and R54 do the same for

U8. These allow the user to minimize the dead-time between one transistor turning off and the other

turning on, thus eliminating any inefficient and potentially damaging large shoot-through currents.

Each trimpot includes a series 20k ohm resistor to ensure that the dead-time resistors are never

shorted. The relative HSG (High Side Gate) and LSG (Low Side Gate) timing diagrams are shown in

Figure 4. Diodes D1 – D4 are used to protect the related pins on the PE29102 to avoid accidental

damage when changing or removing various jumpers. Each PE29102 drives the respective high and

low side E-HEMTs via low value resistors (R8, 25, 10 and 26; R41, 30, 42 and

32)

which tame the parasitic inductances on the transistor gate loops, damping any resonances.

A Zobel network (a.k.a. "Snubber" or "Boucheret Cell") may be connected from each switch node to

ground to tame the high frequency response of the circuit when confronted with a complex reactive