HT46R46/C46/R47/C47/R48A/C48A/R49

Rev. 1.41 10 December 30, 2008

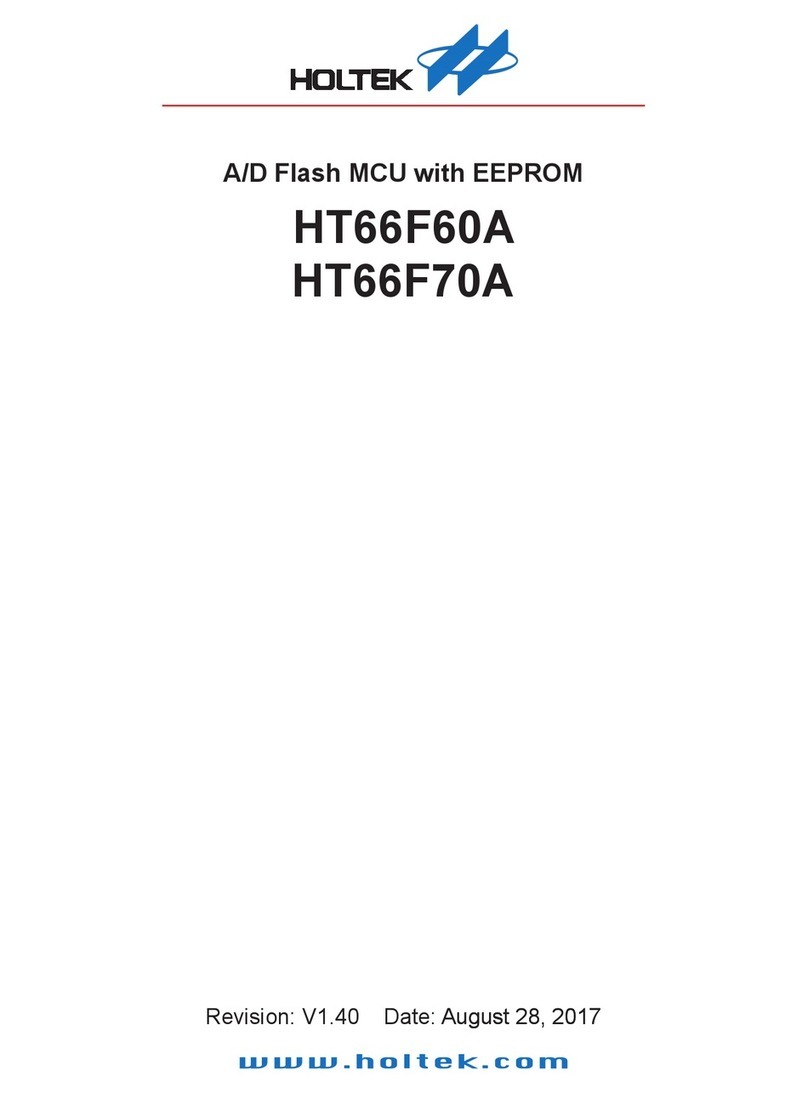

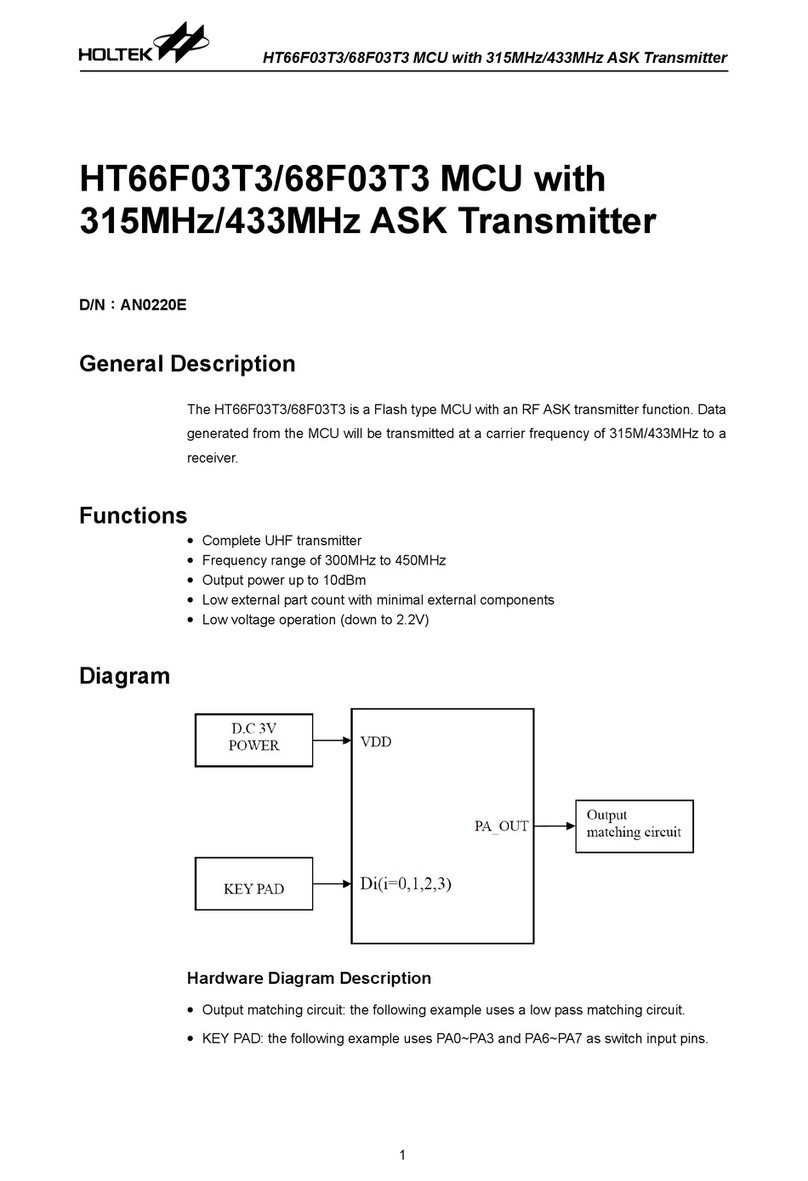

Stack

This is a special part of the memory which is used to

save the contents of the Program Counter only. The

stack can have either 4 or 6 levels depending upon

which device is selected and is neither part of the data

nor part of the program space, and is neither readable

nor writable. The activated level is indexed by the Stack

Pointer, SP, and is neither readable nor writable. At a

subroutine call or interrupt acknowledge signal, the con-

tents of the Program Counter are pushed onto the stack.

At the end of a subroutine or an interrupt routine, sig-

naled by a return instruction, RET or RETI, the Program

Counter is restored to its previous value from the stack.

After a device reset, the Stack Pointer will point to the

top of the stack.

If the stack is full and an enabled interrupt takes place,

the interrupt request flag will be recorded but the ac-

knowledge signal will be inhibited. When the Stack

Pointer is decremented, by RET or RETI, the interrupt

will be serviced. This feature prevents stack overflow al-

lowing the programmer to use the structure more easily.

However, when the stack is full, a CALL subroutine in-

struction can still be executed which will result in a stack

overflow. Precautions should be taken to avoid such

cases which might cause unpredictable program

branching.

Note: For the HT46R46, 4 levels of stack are available

and for the HT46R47,HT46R48A and

HT46R49, 6 levels of stack are available.

Arithmetic and Logic Unit -ALU

The arithmetic-logic unit or ALU is a critical area of the

microcontroller that carries out arithmetic and logic op-

erations of the instruction set. Connected to the main

microcontroller data bus, the ALU receives related in-

struction codes and performs the required arithmetic or

logical operations after which the result will be placed in

the specified register. As these ALU calculation or oper-

ations may result in carry, borrow or other status

changes, the status register will be correspondingly up-

dated to reflect these changes. The ALU supports the

following functions:

·Arithmetic operations: ADD, ADDM, ADC, ADCM,

SUB, SUBM, SBC, SBCM, DAA

·Logic operations: AND, OR, XOR, ANDM, ORM,

XORM, CPL, CPLA

·Rotation RRA, RR, RRCA, RRC, RLA, RL, RLCA,

RLC

·Increment and Decrement INCA, INC, DECA, DEC

·Branch decision, JMP, SZ, SZA, SNZ, SIZ, SDZ,

SIZA, SDZA, CALL, RET, RETI

Program Memory

The Program Memory is the location where the user code

or program is stored. For microcontrollers, two types of

Program Memory are usually supplied. The first type is

the One-Time Programmable, OTP, memory where us-

ers can program their application code into the device.

Devices with OTP memory are denoted by having an ²R²

within their device name. By using the appropriate pro-

gramming tools, OTP devices offer users the flexibility to

freely develop their applications which may be useful

during debug or for products requiring frequent upgrades

or program changes. OTP devices are also applicable for

use in applications that require low or medium volume

production runs. The other type of memory is the mask

ROM memory, denoted by having a ²C²within the device

name. These devices offer the most cost effective solu-

tions for high volume products.

Structure

The Program Memory has a capacity of 1K by 14, 2K by

14 or 4K by 15 bits depending upon which device is se-

lected. The Program Memory is addressed by the Pro-

gram Counter and also contains data, table information

and interrupt entries. Table data, which can be setup in

any location within the Program Memory, is addressed

by separate table pointer registers.

Special Vectors

Within the Program Memory, certain locations are re-

served for special usage such as reset and interrupts.

·Location 000H

This vector is reserved for use by the device reset for

program initialisation. After a device reset is initiated, the

program will jump to this location and begin execution.

·Location 004H

This vector is used by the external interrupt. If the ex-

ternal interrupt pin on the device goes low, the pro-

gram will jump to this location and begin execution if

the external interrupt is enabled and the stack is not

full.

·Location 008H

This internal vector is used by the Timer/Event Coun-

ter. If a counter overflow occurs, the program will jump

to this location and begin execution if the timer/event

counter interrupt is enabled and the stack is not full.

·Location 00CH

This internal vector is used by the A/D converter.

When an A/D conversion cycle is complete, the pro-

gram will jump to this location and begin execution if

the A/D interrupt is enabled and the stack is not full.

P r o g r a m C o u n t e r

S t a c k L e v e l 1

S t a c k L e v e l 2

S t a c k L e v e l 3

S t a c k L e v e l N

P r o g r a m

M e m o r y

T o p o f S t a c k

S t a c k

P o i n t e r

B o t t o m o f S t a c k