Rev. 1.10 7 of 590 November 28, 2018

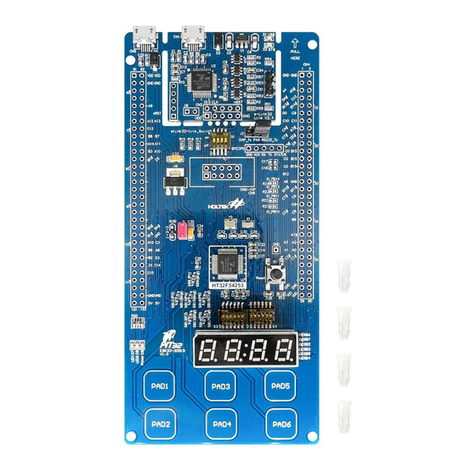

32-Bit Arm®Cortex®-M3 MCU

HT32F12345

Table of Contents

Table of Contents

Data Format and Alignment.......................................................................................................... 190

Analog Watchdog.......................................................................................................................... 190

Interrupts....................................................................................................................................... 190

PDMA Request ............................................................................................................................ 191

Register Map ..................................................................................................................... 191

Register Descriptions......................................................................................................... 193

ADC Reset Register – ADCRST................................................................................................... 193

ADC Regular Conversion Mode Register – ADCCONV ............................................................... 194

ADC High Priority Conversion Mode Register – ADCHCONV...................................................... 195

ADC Regular Conversion List Register 0 – ADCLST0 ................................................................. 196

ADC Regular Conversion List Register 1 – ADCLST1 ................................................................. 197

ADC Regular Conversion List Register 2 – ADCLST2 ................................................................. 198

ADC High Priority Conversion List Register – ADCHLST............................................................. 199

ADC Input Offset Register n – ADCOFRn, n = 0 ~ 11 .................................................................. 200

ADC Input Sampling Time Register n – ADCSTRn, n = 0 ~ 11 .................................................... 201

ADC Regular Conversion Data Register y – ADCDRy, y = 0 ~ 11................................................ 201

ADC High Priority Conversion Data Register y – ADCHDRy, y = 0 ~ 3........................................ 202

ADC Regular Trigger Control Register – ADCTCR....................................................................... 203

ADC Regular Trigger Source Register – ADCTSR ....................................................................... 204

ADC High Priority Trigger Control Register – ADCHTCR ............................................................. 205

ADC High Priority Trigger Source Register – ADCHTSR ............................................................. 206

ADC Watchdog Control Register – ADCWCR .............................................................................. 207

ADC Watchdog Lower Threshold Register – ADCLTR ................................................................. 208

ADC Watchdog Upper Threshold Register – ADCUTR ................................................................ 208

ADC Interrupt Enable Register – ADCIER.................................................................................... 209

ADC Interrupt Raw Status Register – ADCIRAW ......................................................................... 210

ADC Interrupt Status Register – ADCISR......................................................................................211

ADC Interrupt Clear Register – ADCICLR .................................................................................... 213

ADC DMA Request Register – ADCDMAR................................................................................... 214

13 Comparator (CMP) ............................................................................................ 215

Introduction ........................................................................................................................ 215

Features............................................................................................................................. 215

Functional Descriptions ..................................................................................................... 216

Comparator Inputs and Output ..................................................................................................... 216

Comparator Reference Voltage .................................................................................................... 216

Interrupts and Wakeup.................................................................................................................. 217

Power Mode and Hysteresis......................................................................................................... 218

Comparator Write-Protected mechanism ..................................................................................... 218

Register Map ..................................................................................................................... 218

Register Descriptions......................................................................................................... 219

Comparator Control Register n – CMPCRn, n = 0 ~ 1 ................................................................. 219

Comparator Voltage Reference Value Register n – CVRVALRn, n = 0 ~ 1 .................................. 221

Comparator Interrupt Enable Register n – CMPIERn, n = 0 ~ 1................................................... 222

Comparator Transition Flag Register n – CMPTFRn, n = 0 ~ 1.................................................... 223