Rev. 1.00 8 of 486 July 31, 2018

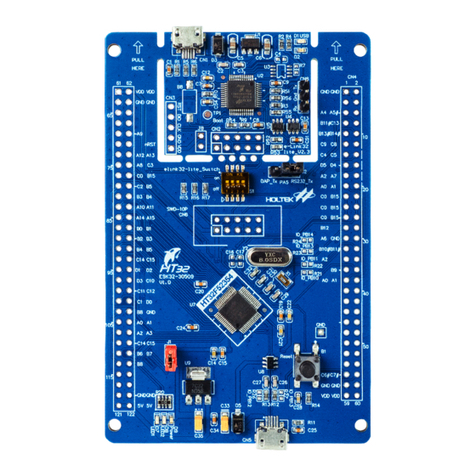

32-Bit Arm®Cortex®-M0+ MCU

HT32F50231/HT32F50241

Table of Contents

Channel 1 Capture / Compare Register – CH1CCR .................................................................... 242

Channel 2 Capture / Compare Register – CH2CCR .................................................................... 243

Channel 3 Capture / Compare Register – CH3CCR .................................................................... 244

Channel 0 Asymmetric Compare Register – CH0ACR................................................................. 245

Channel 1 Asymmetric Compare Register – CH1ACR................................................................. 245

Channel 2 Asymmetric Compare Register – CH2ACR................................................................. 246

Channel 3 Asymmetric Compare Register – CH3ACR................................................................. 246

14 Pulse Width Modulator (PWM)......................................................................... 247

Introduction ........................................................................................................................ 247

Features............................................................................................................................. 248

Functional Descriptions ..................................................................................................... 248

Counter Mode ............................................................................................................................... 248

Clock Controller ............................................................................................................................ 251

Trigger Controller.......................................................................................................................... 252

Slave Controller ............................................................................................................................ 253

Master Controller .......................................................................................................................... 255

Channel Controller........................................................................................................................ 256

Output Stage................................................................................................................................. 256

Update Management .................................................................................................................... 260

Single Pulse Mode........................................................................................................................ 260

Asymmetric PWM Mode ............................................................................................................... 263

Timer Interconnection ................................................................................................................... 263

Trigger Peripherals Start............................................................................................................... 265

Register Map ..................................................................................................................... 266

Register Descriptions......................................................................................................... 267

Timer Counter Conguration Register – CNTCFR ....................................................................... 267

Timer Mode Conguration Register – MDCFR............................................................................. 268

Timer Trigger Conguration Register – TRCFR............................................................................ 271

Timer Counter Register – CTR ..................................................................................................... 272

Channel 0 Output Conguration Register – CH0OCFR ............................................................... 273

Channel 1 Output Conguration Register – CH1OCFR ............................................................... 275

Channel 2 Output Conguration Register – CH2OCFR ............................................................... 277

Channel 3 Output Conguration Register – CH3OCFR ............................................................... 279

Channel Control Register – CHCTR............................................................................................. 281

Channel Polarity Conguration Register – CHPOLR.................................................................... 282

Timer Interrupt Control Register – DICTR .................................................................................... 283

Timer Event Generator Register – EVGR..................................................................................... 284

Timer Interrupt Status Register – INTSR...................................................................................... 285

Timer Counter Register – CNTR................................................................................................... 286

Timer Prescaler Register – PSCR ................................................................................................ 287

Timer Counter Reload Register – CRR ........................................................................................ 287

Channel 0 Compare Register – CH0CR....................................................................................... 288

Channel 1 Compare Register – CH1CR....................................................................................... 288

Channel 2 Compare Register – CH2CR....................................................................................... 289