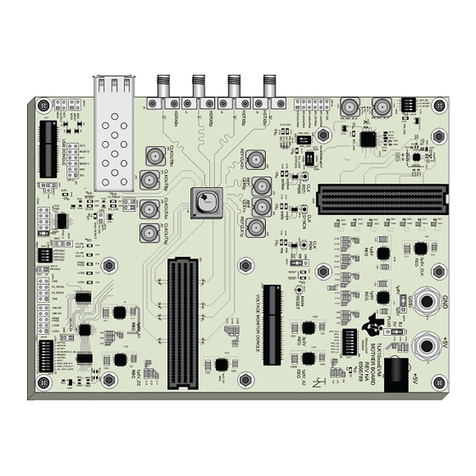

4-4 POWER SUPPLY CIRCUITS

4-4-1 VOLTAGE LINES

LINE DESCRIPTION

Vcc The internal or attached battery pack voltage

or external DC power passed through the

power switch.

-1-5 Common 5Vconverted from the Vcc line at Q1

and Q2 on the REG UNIT using IC1 as the

reference voltage.

-I-5S 5Vcontrolled by the power saver function.

This voltage is converted from Vcc at 03 and

04 on the REG UNIT using IC2 output as the

reference voltage.

R-I-5S Receive 5Vcontrolled by the power saver

function and SEND signal line. This voltage is

converted from Vcc at 05 and 06 on the REG

UNIT using IC3 output as the reference

voltage.

T-l-5 Transmit 5Vcontrolled by the TMUTE signal

line. This voltage is converted from Vcc at 04

and 05 on the APC UNIT.

AF 7VAF amp power source controlled by the AFS

signal line. R14/R15 provides reference

voltage.

4-4-2 CPU POWER SUPPLY CIRCUIT

(LOGIC UNIT)

When the power switch is turned OFF and the

internal/externai battery pack is discharged, avoltage is

appiied to the CPU (IC1) pin 73 via R29 from the iithium

backup battery (BT1) installed In the transceiver to provide

backup for the memory contents.

When the internai or attached battery pack voltage or

external DC power is applied to the transceiver, BT1 is

charged using the current regulator (C3).

4-4-3 +5S AND R+5S SWITCHING

CIRCUITS (REG UNIT)

The IC-2SAT/SET has apower saver to reduce current

consumption to approx. 1/4.

The PSC (Power Saver Control) signal is applied to IC2.

IC2 controls +5S regulator (G3, C4, D1) to turn CN and

CFF +5S voltage.

PSC and SEND signals are applied to ICS. ICS controls

R-t-5S regulator (05, Q6, D2). R+5S turns OFF during

power saved period or transmitting.

4-4-4 CHARGING CIRCUIT (PRT UNIT)

Voltage from the [DC 13.8V] jack is applied to current

control circuit (01, 02, D5, D6) to charge an internal or

attached battery pack (except the BP-85).

When the external battery pack is attached, the current

from D2 charges the attached battery pack. When the

external battery pack is removed, the current from D2

charges the internal battery pack.

The mechanical switch (MP7) selects the battery packs.

This circuit charges one of the battery packs in approx. 15

hours.

Over voltage protector (D4) decreases the transceiver

circuit damage from over voltage and reverse polarity

connections of the power supply.

4-5 OTHER CIRCUITS

4-

5-1 S/RF INDICATOR CIRCUIT

(DET, MAIN AND LOGIC UNITS)

Aportion of the 2nd IF signal is output from IC1 pin 12

on the DET UNIT via the SD signal line. The signal is

rectified at D1 on the MAIN UNIT to obtain an S-indicator

signal. The S-indicator signal is applied to IC2b pin 5

on the LOGIC UNIT.

IC2b pin 6receives an S-indicator reference signal from

the CPU KEYSO—3 terminals via the D/A converter (R11,

R37~R40). The CPU terminals increase the reference

signal level.

When the D/A converted level becomes greater than the

5-

indicator level, IC2b pin 7becomes “LOW.” The CPU

detects the signal strength level using the KEYS0~3

terminal outputs and indicates the signal strength level

on the function display when receiving the “LOW” signal.

While transmitting, the S/RF indicator indicates the

selected output power.

SINDICATOR CIRCUIT

4-5-2 DISPLAY BACKLIGHT CIRCUIT

(LOGIC UNIT)

When the [LIGHT] switch is pushed, pin 77 of the CPU

outputs “HIGH.” The signal is applied to 01 to light up

the backlight LEDs (DS2, DS3).

4—4